What is SoC FPGA Main Characteristic

The challenge of MCUs to application advantages has begun. Field programmable logic devices (FPGAs) with on-chip fixed-function processing subsystems (system-on-a-chip (SoC) FPGAs) have recently become potential competitors for high-end processing applications. in below article will introduce What is SoC FPGA Main Characteristic, this raises the question: As application performance requirements continue to increase, SoC FPGAs will become challengers in a wider range of applications, or will MCUs evolve to better compete with SoC FPGAs? If you are considering a new PCB design, the best method for you now is MCU or SoC FPGA.

Hereby we would like to discuss some of the main advantages and disadvantages of SoC FPGAs compared to MCUs. It will also explore some of the most recent MCU innovations to make it more flexible and better able to address some of the key benefits offered by SoC FPGAs. With this information, you will be able to better choose between MCU and SoC FPGAs in your next PCB board design.

SoC FPGAs combine new flexibility with familiar processing systems

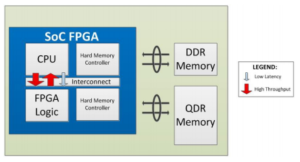

SoC FPGAs combine better in both worlds. For beginners, SoC FPGAs provide a familiar processing system, the CPU, to perform familiar sequential processing algorithms. In fact, many SoC FPGAs have been integrated into the ubiquitous ARM processor architecture to form the basis of their “fixed-function” processing subsystem. This leverages the extensive ecosystem of ARM-compatible tools, intellectual property cores (IP cores) and supporting technologies, making development a very familiar process.

SoC FPGAs also offer flexible, programmable alternatives for sequential processing. The programmable architecture enables you to implement any hardware function you need to enhance the sequential processing power in the processing subsystem. The programmable structure is essentially parallel because multiple hardware modules can operate simultaneously, or in parallel in the case of logical replication, or in a pipelined manner, where the algorithm is divided into phases to handle the overlap. Both methods can produce huge throughput gains compared to sequential methods.