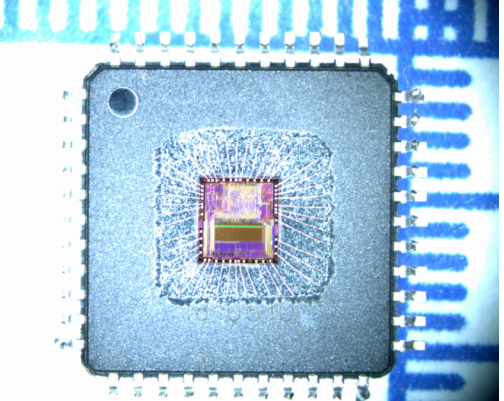

Unlock STM32F103C6 Secured Microprocessor Program

Unlock STM32F103C6 Secured Microprocessor Program from its flash memory, recover embedded firmware from mcu stm32f103c6 flash memory, and then copy heximal software to new stm32f103c6 microcontroller;

The STM32F103C6 family embeds a nested vectored interrupt controller able to handle up to 32 maskable interrupt channels (not including the 16 interrupt lines of Cortex™-M0) and 4 priority levels.

- Closely coupled NVIC gives low latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of late arriving higher priority interrupts

- Support for tail-chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt latency.

The external interrupt/event controller consists of 24 edge detector lines used to generate interrupt/event requests and wake-up the system to clone stm32f103rc mcu software. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently.

A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the internal clock period. Up to 39 GPIOs can be connected to the 16 external interrupt lines.

Tags: descubrir datos de firmware de MCU cifrados,descubrir el código de memoria del chip protegido,descubrir memoria flash de microprocesador segura,descubrir programa heximal microcontrolador bloqueado