Unlock R5F1007EANA#U0 Microcontroller Flash Memory

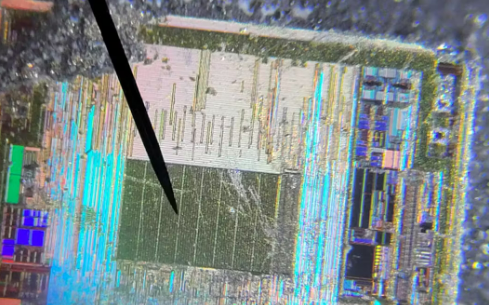

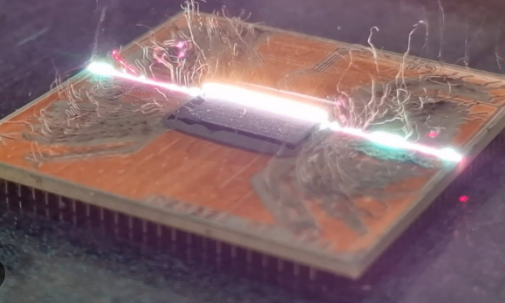

Unlock R5F1007EANA#U0 Microcontroller Flash Memory is a process to faulty injection process, but first of all decapsulation is going to needed to be able to get access to the databus of MCU by microprobe, through power glitch to readout MCU code;

Hereby we would like to introduce some main features of this 16 bits single MCU R5F1007EANA#U0:

Ultra-low power consumption technology

- VDD = single power supply voltage of 1.6 to 5.5 V

- HALT mode

- STOP mode

- SNOOZE mode

RL78 CPU core

- CISC architecture with 3-stage pipeline

- Minimum instruction execution time: Can be changed from high speed (0.03125 μs: @ 32 MHz operation with high- speed on-chip oscillator) to ultra-low speed (30.5 μs: @ 32.768 kHz operation with subsystem clock)

- Address space: 1 MB

- General-purpose registers: (8-bit register × 8) × 4 banks

- On-chip RAM: 2 to 32 KB

Code flash memory

- Code flash memory: 16 to 512 KB

- Block size: 1 KB

- Prohibition of block erase and rewriting (security function)

- On-chip debug function which can be used for Crack microcontroller STM32F103RB flash memory

- Self-programming (with boot swap function/flash shield window function)

Data flash memory

- Data flash memory: 4 KB to 8 KB

- Back ground operation (BGO): Instructions can be executed from the program memory while rewriting the data flash memory for crack R5F10Y47ASP mcu flash memory

- Number of rewrites: 1,000,000 times (TYP.)

- Voltage of rewrites: VDD = 1.8 to 5.5 V

High-speed on-chip oscillator

- Select from 32 MHz, 24 MHz, 16 MHz, 12 MHz, 8 MHz, 6 MHz, 4 MHz, 3 MHz, 2 MHz, and 1 MHz

- High accuracy: ±1.0% (VDD = 1.8 to 5.5 V, TA = -20 to +85°C)

Operating ambient temperature

- TA = -40 to +85°C (A: Consumer applications, D: Industrial applications )

- TA = -40 to +105°C (G: Industrial applications)

Power management and reset function

- On-chip power-on-reset (POR) circuit

- On-chip voltage detector (LVD) (Select interrupt and reset from 14 levels)

Ultra-low power consumption technology

- VDD = single power supply voltage of 1.6 to 5.5 V

- HALT mode

- STOP mode

- SNOOZE mode

RL78 CPU core

- CISC architecture with 3-stage pipeline

- Minimum instruction execution time: Can be changed from high speed (0.03125 μs: @ 32 MHz operation with high- speed on-chip oscillator) to ultra-low speed (30.5 μs: @ 32.768 kHz operation with subsystem clock)

- Address space: 1 MB

- General-purpose registers: (8-bit register × 8) × 4 banks

- On-chip RAM: 2 to 32 KB