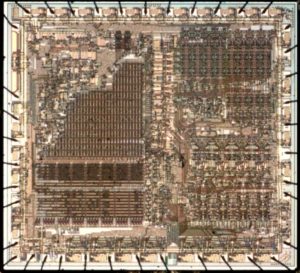

Unlock Philip Chip P87C58 Eprom Code

Acquire the knowledge of counter functions on the timer can bring a lot of benefit to Unlock Philip Chip P87C58 Eprom Code,

In the “Counter” function of Timer 0, the register is incremented in response to a 1-to-0 transition at its corresponding external input pin, T0. In this function, the external input is sampled once during every machine cycle. When the samples of the pin state show a high in one cycle and a low in the next cycle, the count is incremented.

The new count value appears in the register during the cycle following the one in which the transition was detected. Since it takes 2 machine cycles (12 CPU clocks) to recognize a 1-to-0 transition, the maximum count rate is 1/6 of the CPU clock frequency through MCU recovering. There are no restrictions on the duty cycle of the external input signal, but to ensure that a given level is sampled at least once before it changes, it should be held for at least one full machine cycle. The “Timer” or “Counter” function of Timer 0 is selected by control bit C/T in the Special Function Register TMOD.

In addition to the “Timer” or “Counter” selection, Timer 0 and Timer 1 have four operating modes, which are selected by bit-pairs (M1, M0) in TMOD. Modes 0, 1, and 2 are the same for both Timers/Counters. Mode 3 is different. The four operating modes are described in the following text.

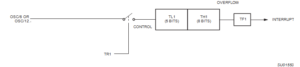

Putting either Timer into Mode 0 makes it look like an 8048 Timer, which is an 8-bit Counter with a divide-by-32 prescaler to achieve the process of NXP MCU P89LPC912 Binary Unlocking. Figures 17 and 18 show Mode 0 operation. In this mode, the Timer register is configured as a 13-bit register. As the count rolls over from all 1s to all 0s, it sets the Timer interrupt flag TFn.

The count input is enabled to Timer 0 when TR0 = 1 and either GATE = 0 or INT0 = 1. (Setting GATE = 1 allows the Timer to be controlled by external input INT0, to facilitate pulse width measurements) after Unlock Philip Chip P87C58 Eprom Code. TRn is a control bit in the Special Function Register TCON (Figure 16). The GATE bit is in the TMOD register (TMOD.3).

The 13-bit register consists of all 8 bits of THn and the lower 5 bits of TLn. The upper 3 bits of TLn are indeterminate and should be ignored. Setting the run flag (TRn) does not clear the registers. Mode 0 operation is slightly different for Timer 0 and Timer 1. See below Figures.