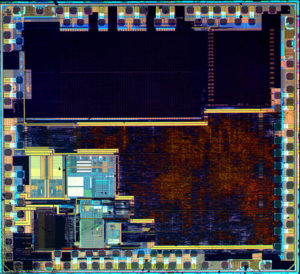

Unlock Microcontroller ATTINY85 Firmware

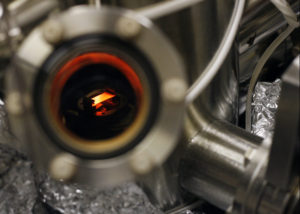

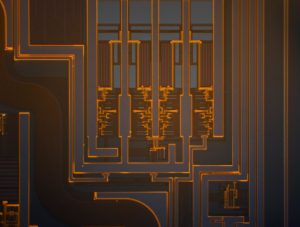

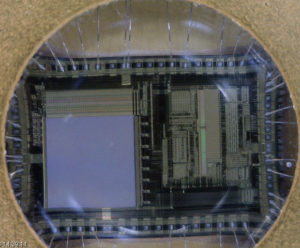

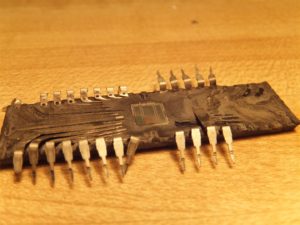

Unlock Microcontroller ATTINY85 and its memory like flash and eeprom content can be readout, program and data will be integrated and dump out together, the microcontroller attiny85 can be read only when the status reset to unlocked one;

Unlock Microcontroller ATTINY85 and its memory like flash and eeprom content can be readout, program and data will be integrated and dump out together,

However, since the USART in MSPIM mode reuses the USART resources, the use of the USART in MSPIM mode is somewhat different compared to the SPI.

In addition to differences of the control register bits, and that only master operation is supported by the USART in MSPIM mode, the following features differ between the two modules:

The USART in MSPIM mode includes (double) buffering of the transmitter. The SPI has no buffer. The USART in MSPIM mode receiver includes an additional buffer level.

The SPI WCOL (Write Collision) bit is not included in USART in MSPIM mode. The SPI double speed mode (SPI2X) bit is not included by mcu reading. However, the same effect is achieved by setting UBRRn accordingly. Interrupt timing is not compatible. Pin control differs due to the master only operation of the USART in MSPIM mode. A comparison of the USART in MSPIM mode and the SPI pins.

Simple yet Powerful and Flexible Communication Interface, only two Bus Lines needed Both Master and Slave Operation Supported

Device can Operate as Transmitter or Receiver 7-bit Address Space

Allows up to 128 Different Slave Addresses

Multi-master Arbitration Support

Up to 400 kHz Data Transfer Speed

Slew-rate Limited Output Drivers

Noise Suppression Circuitry Rejects Spikes on Bus Lines

Fully Programmable Slave Address with General Call Support

Address Recognition Causes Wake-up When AVR is in Sleep Mode

The 2-wire Serial Interface (TWI) is ideally suited for typical microcontroller applications. The TWI protocol allows the systems designer to interconnect up to 128 different devices using only two bi-directional bus lines, one for clock (SCL) and one for data (SDA) .

The only external hardware needed to implement the bus is a single pull-up resistor for each of the TWI bus lines. All devices connected to the bus have individual addresses, and mechanisms for resolving bus contention are inherent in the TWI protocol.

Tags: unlock microcontroller flash archive,unlock microcontroller flash bin,unlock microcontroller flash code,unlock microcontroller flash content,unlock microcontroller flash data,unlock microcontroller flash eeprom,unlock microcontroller flash file,unlock microcontroller flash firmware,unlock microcontroller flash hex,unlock microcontroller flash information,unlock microcontroller flash memory,unlock microcontroller flash program