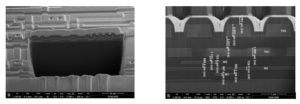

Unlock MCU ATmega324PA Program

Unlock MCU ATmega324PA Program from its flash memory, after decryption process has been completed, the program can be extracted from Microcontroller;

The Stop condition provides a Timer Enable/Disable function. The prescaled CK modes are scaled directly from the CK oscillator clock. If the external pin modes are used for Timer/Counter0, transitions on PB2/(T0) will clock the counter even if the pin is configured as an output.

This feature can give the user SW control of counting. The Timer/Counter0 is implemented as an up-counter with read and write access. If the Timer/Counter0 is written and a clock source is present, the Timer/Counter0 continues counting in the timer clock cycle following the write operation.

This module features a high-resolution and a high-accuracy usage with the lower prescaling opportunities. Timer/Counter1 can also be used as an accurate, high speed, 8-bit Pulse Width Modulator using clock speeds up to 25.6 MHz.

In this mode, Timer/Counter1 and the output compare registers serve as a standalone PWM. Refer to page 34 for a detailed description of this function.

Similarly, the high-prescaling opportunities make this unit useful for lower-speed functions or exact-timing functions with infrequent actions.

The two status flags (overflow and compare match) are found in the Timer/Counter Interrupt Flag Register (TIFR). Control signals are found in the Timer/Counter Control Register (TCCR1). The interrupt enable/disable settings are found in the Timer/Counter Interrupt Mask Register (TIMSK) after Unlock MCU program.

The Timer/Counter1 contains two Output Compare registers, OCR1A and OCR1B, as the data source to be compared with the Timer/Counter1 contents. In normal mode the Output Compare function is operational with OCR1A only, and the Output Compare function includes optional clearing of the counter on compare match, and action on the Output Compare Pin (PB1) (OC1A).

In PWM mode OCR1A provides the data value against which the Timer/Counter value is compared. Upon compare match the PWM output is generated.

In PWM mode The Timer/Counter counts up to the value specified in output compare register OCR1B and starts again from $00. This feature allows limiting the counter “full” value to a specified value, lower than $FF. Together with the many prescaler options, flexible PWM frequency selection is provided.

Table 14 lists clock selection and OCR1B values to obtain PWM frequencies from 10 kHz to 150 kHz at 10 kHz steps.

Tags: unlock mcu dump archive,unlock mcu dump binary,unlock mcu dump code,unlock mcu dump content,unlock mcu dump data,unlock mcu dump eeprom,unlock mcu dump file,unlock mcu dump firmware,unlock mcu dump heximal,unlock mcu dump information,unlock mcu dump memory,unlock mcu dump program