Unlock IC AT89C51ID2 Firmware

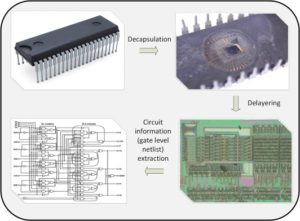

Unlock IC AT89C51ID2 and copy microcontroller at89c51ed2 binary to new mcu which will provide the exact same functions as original version.

The AT89C51ID2 core needs only 6 clock periods per machine cycle. This feature called ‘X2’ provides the following advantages when Unlock IC:

Divide frequency crystals by 2 (cheaper crystals) while keeping same CPU power. Save power consumption while keeping same CPU power (oscillator power saving). Save power consumption by dividing dynamically the operating frequency by 2 in operating and idle modes if Unlock IC.

Increase CPU power by 2 while keeping same crystal frequency. In order to keep the original C51 compatibility, a divider by 2 is inserted between the XTAL1 signal and the main clock input of the core (phase generator). This divider may be disabled by software before Unlock IC.

The clock for the whole circuit and peripherals is first divided by two before being used by the CPU core and the peripherals. This allows any cyclic ratio to be accepted on XTAL1 input. In X2 mode, as this divider is bypassed, the signals on XTAL1 must have a cyclic ratio between 40 to 60%.

Figure 4 shows the clock generation block diagram. X2 bit is validated on the rising edge of the XTAL1÷2 to avoid glitches when switching from X2 to STD mode. Figure 5 shows the switching mode waveforms.

The X2 bit in the CKCON0 register (see Table 20) allows a switch from 12 clock periods per instruction to 6 clock periods and vice versa. At reset, the speed is set according to X2 bit of Hardware Security Byte (HSB). By default, Standard mode is active. Setting the X2 bit activates the X2 feature (X2 mode) if crack pic18lf13k50 memory.

The T0X2, T1X2, T2X2, UartX2, PcaX2, and WdX2 bits in the CKCON0 register (See Table 20.) and SPIX2 bit in the CKCON1 register (see Table 21) allows a switch from standard peripheral speed (12 clock periods per peripheral clock cycle) to fast peripheral speed (6 clock periods per peripheral clock cycle). These bits are active only in X2 mode.

INC is a short (2 bytes) and fast (12 clocks) way to manipulate the DPS bit in the AUXR1 SFR. However, note that the INC instruction does not directly force the DPS bit to a particular state, but simply toggles it. In simple routines, such as the block move example, only the fact that DPS is toggled in the proper sequence matters, not its actual value.

In other words, the block move routine works the same whether DPS is ’0’ or ’1’ on entry. Observe that without the last instruction (INC AUXR1), the routine will exit with DPS in the opposite state.

Tags: unlock ic binary archive,unlock ic binary code,unlock ic binary content,unlock ic binary data,unlock ic binary eeprom,unlock ic binary file,unlock ic binary firmware,unlock ic binary information,unlock ic binary memory,unlock ic binary program