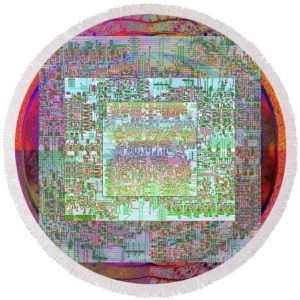

Unlock Chip PIC18F2331 Dump

Unlock Chip PIC18F2331 Dump from its flash and eeprom memory need to learn its features for your reference:

Problem fix/Workaround

Keep the amplified voltage output from the ADC gain stage below 2.4 V in order to get a correct result, or keep ADC voltage reference below 2.4 V.

Sampled BOD in Active mode will cause noise when bandgap is used as reference

Using the BOD in sampled mode when the device is running in Active or Idle mode will add noise on the bandgap reference for ADC, DAC and Analog Comparator

Problem fix/Workaround

If the bandgap is used as reference for either the ADC, DAC and Analog Comparator, the BOD must not be set in sampled mode.

Flash Power Reduction Mode can not be enabled when entering sleep mode

If Flash Power Reduction Mode is enabled when a deep sleep mode, the device will only wake up on every fourth wake-up request. If Flash Power Reduction Mode is enabled when entering Idle sleep mode, the wake-up time will vary with up to 16 CPU clock cycles.

Problem fix/Workaround

Disable Flash Power Reduction mode before entering sleep mode.

JTAG enable does not override Analog Comparator B output

When JTAG is enabled this will not override the Anlog Comparator B (ACB)ouput, AC0OUT on pin 7 if this is enabled.

Problem fix/Workaround

AC0OUT for ACB should not be enabled when JTAG is used. Use only analog comparator output for ACA when JTAG is used, or use the PDI as debug interface.

Bandgap measurement with the ADC is non-functional when VCC is below 2.7V

The ADC cannot be used to do bandgap measurements when VCC is below 2.7V.

Problem fix/Workaround

If internal voltages must be measured when VCC is below 2.7V, measure the internal 1.00V reference instead of the bandgap.

DAC refresh may be blocked in S/H mode

If the DAC is running in Sample and Hold (S/H) mode and conversion for one channel is done at maximum rate (i.e. the DAC is always busy doing conversion for this channel), this will block refresh signals to the second channel.