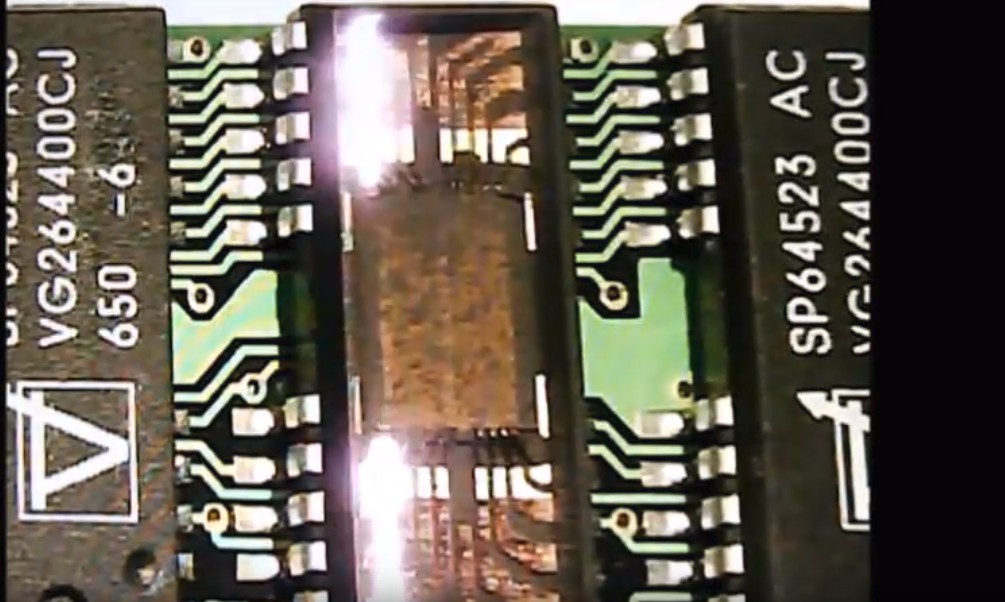

Unlock Chip AT89C5130A Flash

Unlock Chip AT89C5130A Flash memory and readout embedded code from MCU AT89C5130A, through reverse engineering AT89C5130A microcontroller can locate the security fuse bit;

AT89C5130A/31A-M is a high-performance Flash version of the 80C51 single-chip 8-bit microcontrollers with full speed USB functions. AT89C5130A/31A-M features a full-speed USB module compatible with the USB specifications Version 1.1 and 2.0. This module integrates the USB transceivers with a 3.3V voltage regulator and the Serial Interface Engine (SIE) with Digital Phase Locked Loop and 48 MHz clock recovery.

USB Event detection logic (Reset and Suspend/Resume) and FIFO buffers supporting the mandatory control Endpoint (EP0) and up to 6 versatile Endpoints (EP1/EP2/EP3/EP4/EP5/EP6) with minimum software overhead are also part of the USB module before crack chip pic18f4685 hex.

AT89C5130A/31A-M retains the features of the Atmel 80C52 with extended Flash capacity (16/32-Kbytes), 256 bytes of internal RAM, a 4-level interrupt system, two 16-bit timer/counters (T0/T1), a full duplex enhanced UART (EUART) and an on-chip oscillator.

In addition, AT89C5130A/31A-M has an on-chip expanded RAM of 1024 bytes (ERAM), a dual data pointer, a 16-bit up/down Timer (T2), a Programmable Counter Array (PCA), up to 4 programmable LED current sources, a programmable hardware watchdog and a power-on reset when extract mcu pic18f6410 eeprom.

AT89C5130A/31A-M has two software-selectable modes of reduced activity for further reduction in power consumption. In the idle mode the CPU is frozen while the timers, the serial ports and the interrupt system are still operating.

In the power-down mode the RAM is saved, the peripheral clock is frozen, but the device has full wake-up capability through USB events or external interrupts when extract microcontroller pic18f8310 code.

The AT89C5130A/31A-M clock controller is based on an on-chip oscillator feeding an on-chip Phase Lock Loop (PLL). All the internal clocks to the peripherals and CPU core are generated by this controller.

The AT89C5130A/31A-M X1 and X2 pins are the input and the output of a single-stage on-chip inverter (see Figure 5-1) that can be configured with off-chip components as a Pierce oscillator (see Figure 5-2). Value of capacitors and crystal characteristics are detailed in the section “DC Characteristics”.

The X1 pin can also be used as input for an external 48 MHz clock. The clock controller outputs three different clocks as shown in Figure 5-1:

· a clock for the CPU core

· a clock for the peripherals which is used to generate the Timers, PCA, WD, and Port sampling clocks

· a clock for the USB controller

These clocks are enabled or disabled depending on the power reduction mode as detailed in Section “Power Management”, page 155.

Tags: unlock chip heximal archive,unlock chip heximal code,unlock chip heximal content,unlock chip heximal data,unlock chip heximal eeprom,unlock chip heximal file,unlock chip heximal firmware,unlock chip heximal information,unlock chip heximal memory,unlock chip heximal program