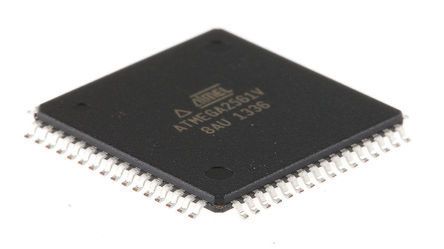

Unlock ATMEGA2561V Microcontroller Flash Memory Content

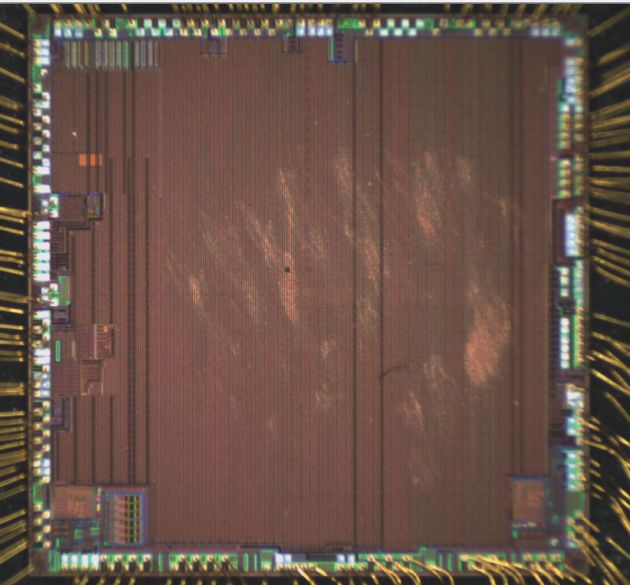

Unlock ATMEGA2561V Microcontroller Flash Memory Content is a process to attack atmel chip atmega2561v security system, and then copy mcu atmega2561v data from its eeprom memory and program from flash memory;

SDA, Two-wire Serial Interface Data: When the TWEN bit in TWCR is set (one) to enable the Two-wire Serial Interface when copy protected atmega32a mcu firmware from its flash memory, pin PC4 is disconnected from the port and becomes the Serial Data I/O pin for the Two-wire Serial Interface.

In this mode, there is a spike filter on the pin to suppress spikes shorter than 50 ns on the input signal when , and the pin is driven by an open drain driver with slew-rate limitation. PC4 can also be used as ADC input Channel 4. Note that ADC input channel 4 uses digital power.

TXD, Transmit Data (Data output pin for the USART). When the USART Transmitter is enabled to prevent the unlocking over secured atmega32u2 processor heximal, this pin is config- ured as an output regardless of the value of DDD1.

RXD, Receive Data (Data input pin for the USART). When the USART Receiver is enabled this pin is configured as an input regardless of the value of DDD0. When the USART forces this pin to be an input, the pull-up can still be controlled by the PORTD0 bit.

The external interrupts are triggered by the INT0, and INT1 pins. Observe that, if enabled, the interrupts will trigger even if the INT0:1 pins are configured as outputs. This feature provides a way of generating a software interrupt. The external interrupts can be triggered by a falling or rising edge or a low level.