Unlock ATMEGA128 Microcontroller Flash Heximal

Unlock ATMEGA128 Microcontroller Flash Heximal and break off the security fuse bit of microprocessor atmega128, extract embedded binary from atmega128 MCU;

This bit is set if a Power-on Reset occurs. The bit is reset only by writing a logic zero to the flag. To make use of the Reset Flags to identify a reset condition, the user should read and then reset the MCUCSR as early as possible in the program. If the register is cleared before another reset occurs, the source of the reset can be found by examining the Reset Flags.

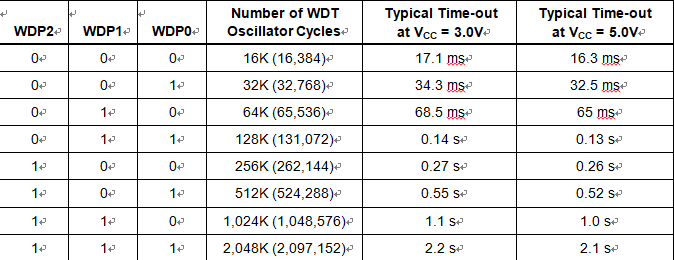

This bit must be set when the WDE bit is written to logic zero. Otherwise, the Watchdog will not be disabled. Once written to one, hardware will clear this bit after four clock cycles when recover atmega64 mcu flash embedded heximal. Refer to the description of the WDE bit for a Watchdog disable procedure. In Safety Level 1 and 2, this bit must also be set when changing the prescaler bits.

When the WDE is written to logic one, the Watchdog Timer is enabled, and if the WDE is written to logic zero, the Watchdog Timer function is disabled. WDE can only be cleared if the WDCE bit has logic level one to restore atmega64l microcontroller flash software. To disable an enabled Watchdog Timer, the following procedure must be followed:

- In the same operation, write a logic one to WDCE and WDE. A logic one must be written to WDE even though it is set to one before the disable operation starts.

- Within the next four clock cycles, write a logic 0 to WDE. This disables the Watchdog.

Tags: sbloccare atmega128 dati esagonali protetti della eeprom del microcontrollore,sbloccare atmega128 file binario di memoria del microcomputer protetto,sbloccare atmega128 programma firmware integrato MCU IC crittografato,sbloccare atmega128 software di memoria flash del microprocessore bloccato