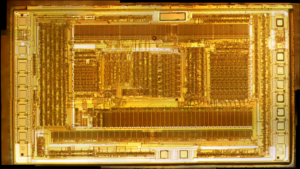

ST62T46 Chip Source Code Extraction

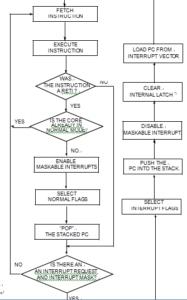

The ST6 core may be interrupted by four maskable interrupt sources through which can effectively help to carry out ST62T46 Chip Source Code Extraction, in addition to a Non Maskable Interrupt (NMI) source. The interrupt processing flowchart is shown in below Figure.

Maskable interrupts must be enabled by setting the GEN bit in the IOR register. However, even if they are disabled (GEN bit = 0), interrupt events are latched and may be processed as soon as the GEN bit is set.

Each source is associated with a specific Interrupt Vector, located in Program space. In the vector location, the user must write a Jump in-struction to the associated interrupt service routine. When an interrupt source generates an interrupt request in order to Read Microcontroller ST62T52 Dump, the PC register is loaded with the address of the interrupt vector, which then causes a Jump to the relevant interrupt service routine, thus serv- icing the interrupt.

Interrupt are triggered by events either on external pins, or from the on-chip peripherals. Several events can be ORed on the same interrupt vector. On-chip peripherals have flag registers to determine which event triggered the interrupt.

ST62T46 Chip Source Code Extraction

A Reset can interrupt the NMI and peripheral interrupt routines

The Non-Maskable Interrupt request has the highest priority and can interrupt any peripheral interrupt routine at any time but cannot interrupt another NMI interrupt to facilitate Locked ST62T09 Heximal Cloning.

No peripheral interrupt can interrupt another. If more than one interrupt request is pending, these are processed by the processor core according to their priority level: vector #1 has the highest priority while vector #4 the lowest. The priority of each interrupt source is fixed by hardware (see Interrupt Mapping table).