Reverse Engineering AVR Chip atmel ATtiny12L

Reverse Engineering AVR Chip atmel ATtiny12L

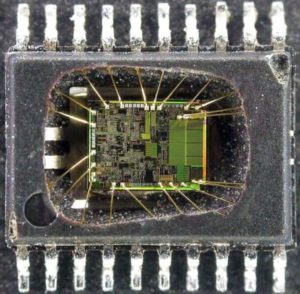

Reverse Engineering AVR Chip atmel ATtiny12L needs to understand the construction of ATtiny12L and delayer the microcontroller in the counter sequence of chip manufacturing:

Features

· Utilizes the AVR® RISC Architecture

· AVR – High-performance and Low-power RISC Architecture

– 90 Powerful Instructions – Most Single Clock Cycle Execution

– 32 x 8 General-purpose Working Registers

– Up to 4 MIPS Throughput at 4 MHz

Nonvolatile Program Memory

– 2K Bytes of Flash Program Memory

– Programming Lock for Flash Program Data Security

Peripheral Features

– Interrupt and Wake-up on Low-level Input

– One 8-bit Timer/Counter with Separate Prescaler

– Programmable Watchdog Timer with On-chip Oscillator

– Built-in High-current LED Driver with Programmable Modulation

Special Microcontroller Features

– Low-power Idle and Power-down Modes

– External and Internal Interrupt Sources

– Power-on Reset Circuit with Programmable Start-up Time

– Internal Calibrated RC Oscillator

Power Consumption at 1 MHz, 2V, 25°C

– Active: 3.0 mA

– Idle Mode: 1.2 mA

– Power-down Mode: <1 µA

– 11 Programmable I/O Lines, 8 Input Lines and a High-current LED Driver

– 28-lead PDIP, 32-lead TQFP, and 32-pad MLF

8-bit Microcontroller with 2K Bytes of Flash

ATtiny28L

ATtiny28V

Summary

– 0 – 1.2 MHz for the ATtiny28V