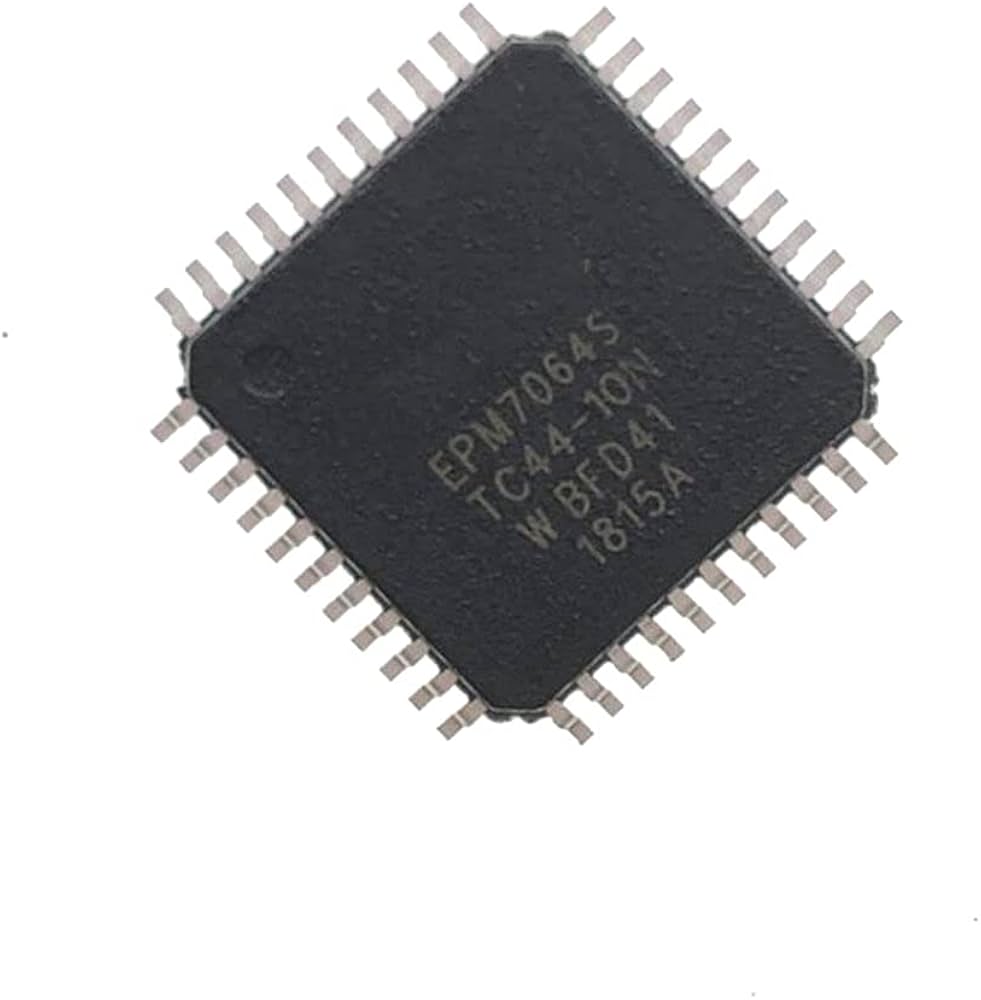

Retrieve IC Altera CPLD EPM7064STC44-10

The Altera CPLD EPM7064STC44-10 is a widely utilized Complex Programmable Logic Device (CPLD) known for its reliability in timing-critical, low-power embedded applications. It plays a crucial role in controlling logic, interfaces, and custom digital functions in both consumer and industrial electronics. Due to its flexible architecture and programmability, it often stores proprietary firmware, configuration data, and logic files that are considered highly valuable and often secured or protected against unauthorized access.

When an organization or technician faces a case of lost firmware, source code, or original program archive, there may arise a critical need to retrieve or extract the data from the locked CPLD. This could be required for system maintenance, duplication of legacy hardware, reverse-engineering for interoperability, or forensic analysis. However, retrieving the IC Altera CPLD EPM7064STC44-10 is not a simple process and presents multiple technical challenges due to its robust security measures.

Challenges in Retrieving Data from EPM7064STC44-10

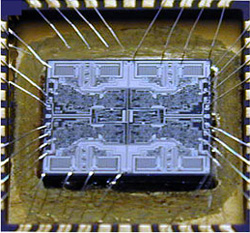

The EPM7064STC44-10 is designed with a set of hardware-level protections that make readout, cloning, or duplication extremely difficult. Once the chip is configured and security bits are enabled, its internal memory becomes locked, preventing normal access to the binary configuration files or EEPROM-based logic.

We can Retrieve IC Altera CPLD EPM7064STC44-10 from its encrypted situation, please view below chip features for your reference:

High-performance, EEPROM-based programmable logic devices (PLDs) based on second-generation MAX® architecture

5.0-V in-system programmability (ISP) through the built-in IEEE Std. 1149.1 Joint Test Action Group (JTAG) interface available in MAX 7000S devices

– ISP circuitry compatible with IEEE Std. 1532

Includes 5.0-V MAX 7000 devices and 5.0-V ISP-based MAX 7000S devices

Built-in JTAG boundary-scan test (BST) circuitry in MAX 7000S devices with 128 or more macrocells

Complete EPLD family with logic densities ranging from 600 to 5,000 usable gates 5-ns pin-to-pin logic delays with up to 175.4-MHz counter frequencies (including interconnect) PCI-compliant devices available.