Replicate Philip Microcontroller P87C754 Flash Code

Replicate Philip Microcontroller P87C754 Flash Code needs to knows how the watchdog is functioning:

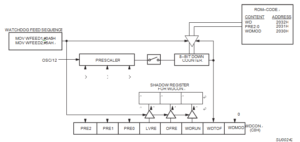

When the watchdog is in the watchdog mode and the watchdog underflows, the following action takes place (see below Figure):

• Autoload takes place.

• Watchdog time-out flag is set

• Mode bit unchanged.

• Watchdog run bit unchanged.

• Autoload register unchanged.

• Prescaler tap unchanged.

• All other device action same as external reset.

Note that if the watchdog underflows, the program counter will start from 00H as in the case of an external reset. The watchdog time-out flag can be examined to determine if the watchdog has caused the reset condition. The watchdog time-out flag bit can be cleared by software which has the similar features of Philip MCU P87C752 Memory Code extraction.

When the watchdog is in the timer mode and the timer software underflows, the following action takes place:

• Autoload takes place.

• Watchdog time-out flag is set

• Mode bit unchanged.

• Watchdog run bit unchanged.

• Autoload register unchanged.

• Prescaler tap unchanged.

Mask ROM Device (EA = 1)

In the mask ROM device, the watchdog mode bit (WDMOD) is mask programmed and the bit in the watchdog command register is read only and reflects the mask programmed selection. If the mask programmed mode bit selects the timer mode, then the watchdog run bit (WDRUN) operates as described under EPROM MCU Reading. If the mask programmed bit selects the watchdog mode, then the watchdog run bit has no effect on the timer operation.

Watchdog Function

The watchdog consists of a programmable prescaler and the main timer. The prescaler derives its clock from the on-chip oscillator. The prescaler consists of a divide by 12 followed by a 13 stage counter with taps from stage 6 through stage 13. This is shown in Figure 17. The tap selection is programmable.

The watchdog main counter is a down counter clocked (decremented) each time the programmable prescaler underflows. The watchdog generates an underflow signal (and is autoloaded) when the watchdog is at count 0 and the clock to decrement the watchdog occurs.

The watchdog is 8 bits long and the autoload value can range from 0 to FFH. (The autoload value of 0 is permissible since the prescaler is cleared upon autoload). This leads to the following user design equations.