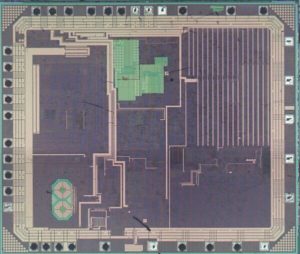

Renesas R5F64110DFB Microcontroller Flash Program Cloning

Renesas R5F64110DFB Microcontroller Flash Program Cloning is a process through which the firmware embedded in the microcomputer’s R5F64110DFB#U0 can be extracted and copy into blank MCU after microcontroller reverse engineering:

The R5F64110DFB#U0 CPU supports eight addressing modes. Each instruction uses a subset of these addressing modes, through this modes we will be able to find the right path for cloning MCU R5F64110DFB#U0 program;

(1) Register Direct—Rn: The register field of the instruction specifies an 8- or 16-bit general register containing the operand. In most cases the general register is accessed as an 8-bit register for the purpose of Microcontroller ST62T40 Flash Program Cloning. Only the MOV.W, ADD.W, SUB.W, CMP.W, ADDS, SUBS, MULXU (8 bits 8 bits), and DIVXU (16 bits 8 bits) instructions have 16-bit operands.

(2) Register Indirect—@Rn: The register field of the instruction specifies a 16-bit general register containing the address of the operand.

(3) Register Indirect with Displacement—@(d:16, Rn): This mode, which is used only in MOV instructions, is similar to register indirect but the instruction has a second word (bytes 3 and

(4) which is added to the contents of the specified general register to obtain the operand address. For the MOV.W instruction, the resulting address must be even. Register Indirect with Post-Increment or Pre-Decrement—@Rn+ or @–Rn:

• Register indirect with Post-Increment—@Rn+

The @–Rn mode is used with MOV instructions that store register contents to memory.

It is similar to the register indirect mode, but the 16-bit general register specified in the register field of the instruction is decremented before the operand is accessed by Decoding STM32F100VD Microcontroller Flash Program. The size of the decrement is 1 or 2 depending on the size of the operand: 1 for MOV.B; 2 for MOV.W. For MOV.W, the original contents of the 16-bit general register must be even.