Readout Altera CPLD EPM7032SLC44-6 Eeprom JED Data

Readout Altera CPLD EPM7032SLC44-6 Eeprom JED Data and the original cpld altera epm7032slc44 will be reverse engineered, eeprom data of cpld chip epm7032slc44 will be extracted;

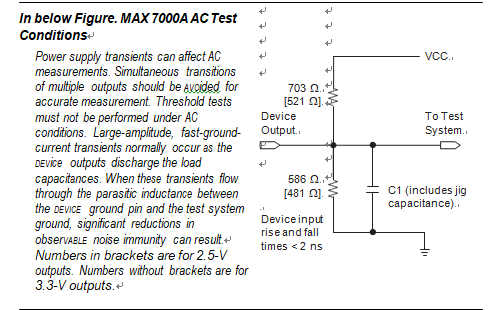

MAX 7000A devices are fully tested. Complete testing of each

programmable EEPROM bit and all internal logic elements ensures 100% programming yield. AC test measurements are taken under conditions equivalent to those shown in below Figure. Test patterns can be used and then erased during early stages of the production flow.

MAX 7000A device timing can be analyzed with the Altera software, a variety of popular industry-standard EDA simulators and timing analyzers, or with the timing model shown in Figure 11.

MAX 7000A devices have predictable internal delays that enable the designer to determine the worst-case timing of any design when copying pld epm7032blc44 eeprom pof file. The software provides timing simulation, point-to-point delay prediction, and detailed timing analysis for device-wide performance evaluation.

The timing characteristics of any signal path can be derived from the timing model and parameters of a particular device. External timing parameters, which represent pin-to-pin timing delays in the process of cloning altera epm7032vlc44 cpld eeprom firmware, can be calculated as the sum of internal parameters. Below Figure shows the timing relationship between internal and external delay parameters.