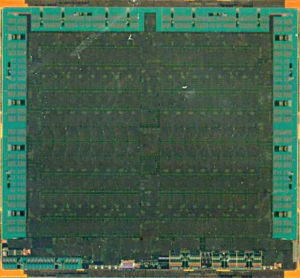

Read Microcomputer Maxim DS5250

Read Microcomputer Maxim DS5250

Read Microcomputer Maxim DS5250 embedded firmware

GENERAL DESCRIPTION

The DS5250 is a highly secure, 4 clocks-per-machine cycle, 100% 8051-instruction-set-compatible microprocessor in the Secure Microcontroller family from Dallas Semiconductor. It was designed to be the cryptographic engine of PIN pads, financial terminals, and any other application in which data security is paramount. A key feature of the device is that it encrypts its program memory with a hardware-based single or triple (3) DES (data encryption standard) algorithm, making it nearly impossible to extract information. Another DES (3DES) hardware block is available to the user for encrypting arbitrary information in data memory space. This makes the device ideal for storage and transmission of passwords, personal identification numbers, encryption keys, and other highly confidential information.

FEATURES

Drop-In Upgrade to the Dallas DS5240

Feature-Rich, 8051-Compatible, Highly Secure Microcontroller

Built-In Sensors Detect Attack and Cause Security Response

Programmable Attack Countermeasures

Secure Bootstrap Loader

True Random-Number Generator (RNG)

Accesses Up to 4MB Program and 4MB Data Memory (All Nonvolatile)

In-System Programmable through Serial Port

In-Application Programmable through User Software;

Allows Self-Modification of Program/Data Memory

Four 8-Bit Ports/One 6-Bit Port

Three 16-Bit Timer/Counters

256 Bytes of Scratchpad RAM

Advanced Features

5kB Internal SRAM (Optional 1kB Stack)

Single or 3DES Engine

Partitionable Memory Segments Variable from 4kB to

256kB

High-Speed Architecture

4 Clocks-per-Machine Cycle

DC-to-25MHz Operation

Single-Cycle Instruction in 160ns

Dual Data Pointers can Increment or Decrement

Independently

Automatic Data Pointer Selection Available

Programmable Speed MOVX Instructions

1kB On-Chip Instruction Cache

High-Reliability Operation

Early-Warning Power-Fail Interrupt

Watchdog Timer

Nonvolatile Functions

On-Chip Real-Time Clock with Alarm Interrupt

2kB Battery-Backed Internal SRAM

Security Features

Designed to Meet the Physical Security Requirements of FIPS-140 and Common Criteria Certifications

Program Memory Integrity Checking

Executes Single/3DES-Encrypted Programs to Prevent Observation

Separate Program/Data Cryptograph Two Self-Destruct Inputs 4096-Bit Modulo-Arithmetic Accelerator (MAA) for PKI Operations

Pin Configurations appear on page 2. rity

Response

Programmable Attack Countermeasures

Secure Bootstrap Loader

True Random-Number Generator (RNG)

Unique ID Number in Every Device