Read MCU PIC16F946 Program

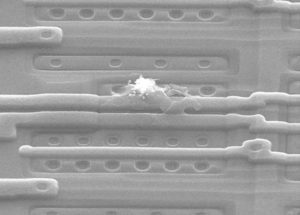

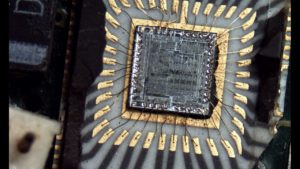

Read MCU PIC16F946 Program and copy the firmware into blank Microcontroller PIC16F946, this is a whole process of IC breaking which can help engineer to recover Microprocessor memory program out;

Read MCU PIC16F946 Program and copy the firmware into blank Microcontroller PIC16F946, this is a whole process of IC breaking which can help engineer to recover Microprocessor memory program out

The AUSART will remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore cannot generate the necessary signals to run the Transmit or Receive Shift registers during Sleep. Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

9.4.1 SYNCHRONOUS RECEIVE DURING SLEEP

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

· RCSTA and TXSTA Control registers must be configured for Synchronous Slave Reception (see Section 9.3.2.4 “Synchronous Slave Reception Set-up:”).

· If interrupts are desired, set the RCIE bit of the PIE1 register and the PEIE bit of the INTCON register after breaking microchip mcu pic16lf877.

· The RCIF interrupt flag must be cleared by reading RCREG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RX/DT and TX/CK pins, respectively. When the data word has been completely clocked in by the external device, the RCIF interrupt flag bit of the PIR1 register will be set. Thereby, waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the GIE global interrupt enable bit of the INTCON register is also set, then the Interrupt Service Routine at address 004h will be called.

9.4.2 SYNCHRONOUS TRANSMIT DURING SLEEP

To transmit during Sleep, all the following conditions must be met before entering Sleep mode:

· RCSTA and TXSTA Control registers must be configured for Synchronous Slave Transmission (see Section 9.3.2.2 “Synchronous Slave Transmission Set-up:”).

· The TXIF interrupt flag must be cleared by writing the output data to the TXREG, thereby filling the TSR and transmit buffer.

If interrupts are desired, set the TXIE bit of the PIE1 register and the PEIE bit of the INTCON register for the purpose of avr atmega165 hacking.

Upon entering Sleep mode, the device will be ready to accept clocks on TX/CK pin and transmit data on the RX/DT pin. When the data word in the TSR has been completely clocked out by the external device, the pending byte in the TXREG will transfer to the TSR and the TXIF flag will be set. Thereby, waking the processor from Sleep. At this point, the TXREG is available to accept another character for transmission, which will clear the TXIF flag.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the GIE global interrupt enable bit is also set then the Interrupt Service Routine at address 0004h will be called.

Tags: read mcu locked archive,read mcu locked code,read mcu locked content,read mcu locked data,read mcu locked eeprom,read mcu locked file,read mcu locked firmware,read mcu locked information,read mcu locked memory,read mcu locked program