Philip Chip P89V51RC2 Dump Reading

Philip Chip P89V51RC2 Dump Reading will provide the direct effect on the program memory from flash and eeprom area, and there are two internal flash memory blocks in the device. Block 0 has 16/32/64 kB and is organized as 128/256/512 sectors, each sector consists of 128 Bytes.

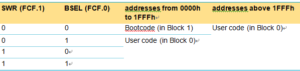

Block 1 contains the IAP/ISP routines and may be enabled such that it overlays the first 8 kB of the user code memory. The overlay function is controlled by the combination of the Software Reset Bit (SWR) at FCF.1 and the Bank Select Bit (BSEL) at FCF.0. The combination of these bits and the memory source used for instructions is shown in below Table.

Access to the IAP routines in Block 1 may be enabled by clearing the BSEL bit (FCF.0), provided that the SWR bit (FCF.1) is cleared. Following a power-on sequence, the bootcode is automatically executed and attempts to autobaud to a host.

If no autobaud occurs within approximately 400 ms and the SoftICE flag is not set, control will be passed to the user code. A software reset is used to accomplish this control transfer and as a result the SWR bit will remain set. Therefore the user’s code will need to clear the SWR bit in order to access the IAP routines in Block only after the process of Microcontroller P89LV51 Embedded Firmware cloning has been completed.

1. However, caution must be taken when dynamically changing the BSEL bit. Since this will cause different physical memory to be mapped to the logical program address space, the user must avoid clearing the BSEL bit when executing user code MCU Reading within the address range 0000H to 1FFFH.