NXP MCU P89LPC912 Binary Unlocking

NXP MCU P89LPC912 Binary Unlocking

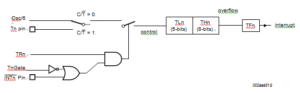

NXP MCU P89LPC912 Binary Unlocking refers to disable the timer and send out the manipulated signals to the timer, Putting either Timer into Mode 0 makes it look like an 8048 Timer, which is an 8-bit Counter with a fixed divide-by-32 prescaler. Below Figure shows Mode 0 operation.

In this mode, the Timer register is configured as a 13-bit register. As the count rolls over from all 1s to all 0s, it sets the Timer interrupt flag TFn. The count input is enabled to the Timer when TRn = 1 and either GATE = 0 or INTn = 1. (Setting GATE = 1 allows the Timer to be controlled by external input INTn, to facilitate pulse width measurements). TRn is a control bit in the Special Function Register TCON. The GATE bit is in the TMOD register.

The 13-bit register consists of all 8 bits of THn and the lower 5 bits of TLn. The upper 3 bits of TLn are indeterminate and should be ignored. Setting the run flag (TRn) does not clear the registers.

Mode 0 operation is the same for Timer 0 and Timer 1 (see above Figure). There are two different GATE bits, one for Timer 1 (TMOD.7) and one for Timer 0 (TMOD.3).

Mode 1 is the same as Mode 0, except that all 16 bits of the timer register (THn and TLn) are used.

Mode 2 configures the Timer register as an 8-bit Counter (TLn) with automatic reload, as shown in below Figure. Overflow from TLn not only sets TFn, but also reloads TLn with the contents of THn, which must be preset by software. The reload leaves THn unchanged. Mode 2 operation is the same for Timer 0 and Timer 1.