Microprocessor ST7FLITE39F2B6 Embedded Firmware Cloning

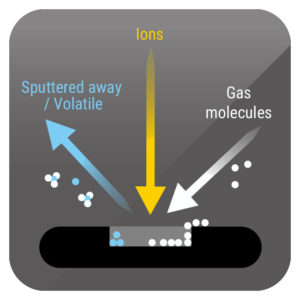

Microprocessor ST7FLITE39F2B6 Embedded Firmware Cloning can be realized if maskable sources is traceble through the microprobing technique:

Maskable interrupt vector sources can be serviced if the corresponding interrupt is enabled and if its own interrupt software priority (in ISPRx registers) is higher than the one currently being serviced (I1 and I0 in CC register). If any of these two condi- tions is false, the interrupt is latched and thus re- mains pending.

MCES (MTC Emergency Stop)

This hardware interrupt occurs when a specific edge is detected on the dedicated MCES pin or when an error is detected by the micro in the motor speed measurement. The interrupt request is maintained to unlock NXP MCU P87C554 Embedded Firmware as long as the MCES pin is low if the interrupt is enabled by the EIM bit in the MIMR register.

External Interrupts

External interrupts allow the processor to exit from Halt low power mode.

External interrupt sensitivity is software selectable through the External Interrupt Control register (EICR).

External interrupt triggered on edge will be latched and the interrupt request automatically cleared upon entering the interrupt service routine.

If several input pins of a group connected to the same interrupt line are selected simultaneously, these will be logically ORed.

Peripheral Interrupts

Usually the peripheral interrupts cause the MCU to exit from Halt mode except those mentioned in the “Interrupt Mapping” table.

A peripheral interrupt occurs when a specific flag is set in the peripheral status registers and if the corresponding enable bit is set in the peripheral control register.

The general sequence for clearing an interrupt is based on an access to the status register followed by a read or write to an associated register when break IC eeprom. Note: The clearing sequence resets the internal latch. A pending interrupt (i.e. waiting for being serviced) will therefore be lost if the clear se- quence is executed.