Microcontroller ST7FLITE39F2M6 Heximal Unlocking

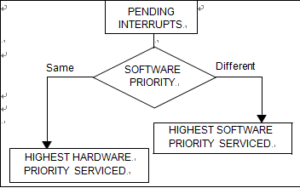

Microcontroller ST7FLITE39F2M6 Heximal Unlocking need to have knowledge about its interrupt especially the servicing pending interrupt, as several interrupts can be pending at the same time, the interrupt to be taken into account is deter- mined by the following two-step process:

the highest software priority interrupt is serviced,

if several interrupts have the same software pri- ority then the interrupt with the highest hardware priority is serviced.

Below Figure describes this decision process.

When an interrupt request is not serviced immediately, it is latched and then processed when its software priority combined with the hardware priority becomes the highest one in the process of MCU ST7FLITEBCM6 Locked Eeprom Memory cracking.

Note 1: The hardware priority is exclusive while the software one is not. This allows the previous process to succeed with only one interrupt.

Note 2: RESET, TRAP and MCES can be considered as having the highest software priority in the decision process.

There are different interrupt vector sources, two interrupt source types are managed by the ST7 interrupt controller: the non-maskable type (RESET, TRAP) and the maskable type (external or from internal peripherals).

also the NON-MASKABLE SOURCES, These sources are processed regardless of the state of the I1 and I0 bits of the CC register (see above Figure). After stacking the PC, X, A and CC registers (except for RESET), the corresponding vector is loaded in the PC register and the I1 and I0 bits of the CC are set to disable interrupts and break IC flash (level 3). These sources allow the processor to exit Halt mode.

n TRAP (Non Maskable Software Interrupt)

This software interrupt is serviced when the TRAP instruction is executed. It will be serviced according to the flowchart in above Figure as a MCES top level interrupt.