Microcontroller ATMEGA64L Flash Software Restoration

Microcontroller ATMEGA64L Flash Software Restoration refers to attack atmega64l avr chip memory protection, and then read embedded firmware out from mcu atmega64l;

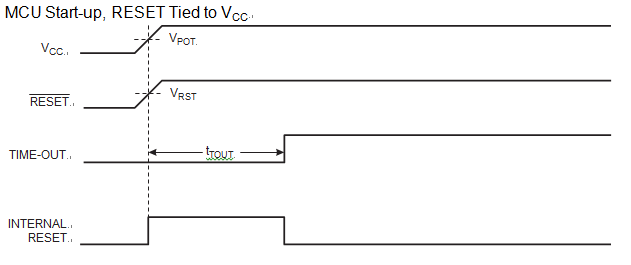

A Power-on Reset (POR) pulse is generated by an On-chip detection circuit. The detection level is defined in Table 26-3 on page 235. The POR is activated whenever VCC is below the detection level.

The POR circuit can be used to trigger the Start-up Reset, as well as to detect a failure in supply voltage. A Power-on Reset (POR) circuit ensures that the device is reset from Power-on.

Reaching the Power-on Reset threshold voltage invokes the delay counter, which determines how long the device is kept in RESET after VCC rise. The RESET signal is activated again, without any delay, when VCC decreases below the detection level.

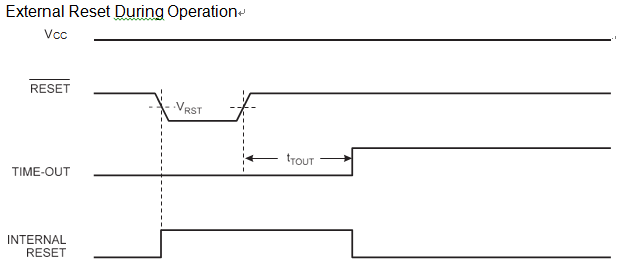

An External Reset is generated by a low level on the RESET pin. Reset pulses longer than the minimum pulse width (see Table 26-3 on page 235) will generate a reset, even if the clock is not running. Shorter pulses are not guaranteed to generate a reset.

When the applied signal reaches the Reset Threshold Voltage – VRST on its posi- tive edge, the delay counter starts the MCU after the time-out period tTOUT has expired.

Tags: rétablir atmega64l fichier binaire de mémoire de micro-ordinateur sécurisé,rétablir atmega64l logiciel de mémoire flash à microprocesseur verrouillé,rétablir atmega64l microcontrôleur protégé eeprom données heximales,rétablir atmega64l programme de micrologiciel intégré MCU IC crypté