Extract CPLD Lattice ISPLSI1024

We can Extract CPLD Lattice ISPLSI1024, please view below chip features for your reference:

· HIGH DENSITY PROGRAMMABLE LOGIC

— 4000 PLD Gates

— 48 I/O Pins, Two Dedicated Inputs

— 144 Register

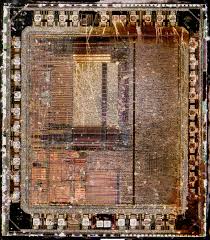

Functional Block Diagram

— High Speed Global Interconnect

— Wide Input Gating for Fast Counters, State Machines, Address Decoders, etc. Small Logic Block Size for Random Logic

· NEW FEATURES

— 100% IEEE 1149.1 Boundary Scan Testable

— ispJTAG™ In-System Programmable via IEEE 1149.1 (JTAG) Test Access Port

— User Selectable 3.3V or 5V I/O Supports Mixed-Voltage Systems (VCCIO Pin)

— Open-Drain Output Option

· HIGH PERFORMANCE E2CMOS® TECHNOLOGY

— fmax = 200 MHz Maximum Operating Frequency

— tpd = 4.5 ns Propagation Delay

— TTL Compatible Inputs and Outputs

— Electrically Erasable and Reprogrammable

— Non-Volatile

— 100% Tested at Time of Manufacture

— Unused Product Term Shutdown Saves Power

· IN-SYSTEM PROGRAMMABLE

— Increased Manufacturing Yields, Reduced Time-to-Market and Improved Product Quality

— Reprogram Soldered Devices for Faster Prototyping

· OFFERS THE EASE OF USE AND FAST SYSTEM

SPEED OF PLDs WITH THE DENSITY AND FLEXIBILITY

OF FIELD PROGRAMMABLE GATE ARRAYS

— Complete Programmable Device Can Combine Glue

Logic and Structured Designs

— Enhanced Pin Locking Capability

— Four Dedicated Clock Input Pins

— Synchronous and Asynchronous Clocks

— Programmable Output Slew Rate Control to Minimize Switching Noise

— Flexible Pin Placement

— Optimized Global Routing Pool Provides Global Interconnectivity

Tags: extract cpld code,extract cpld content,extract cpld firmware,extract cpld flash,extract cpld memory,extract cpld program,mal humor интегрална схема lotsked binary,mal humor интегрална схема lotsked code,mal humor интегрална схема lotsked data,mal humor интегрална схема lotsked eeprom,mal humor интегрална схема lotsked file,mal humor интегрална схема lotsked firmware,mal humor интегрална схема lotsked heximal,mal humor интегрална схема lotsked memory,mal humor интегрална схема lotsked program