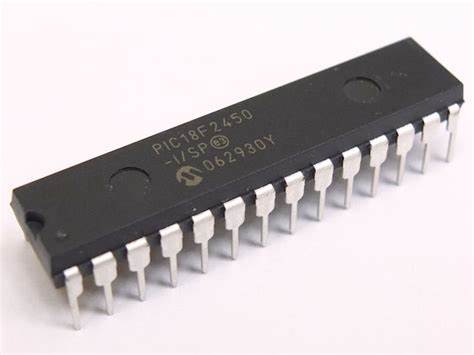

Duplicate Microchip PIC18F2450T Microcontroller Flash Software

Duplicate Microchip PIC18F2450T Microcontroller Flash Software needs to break locked fuse bit of microcontroller pic18f2450t and read protected heximal file out from pic18f2450t microprocessor;

When operating in Asynchronous mode, the EUSART module consists of the following important elements:

- Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

- Auto-Wake-up on Sync Break Character

- 12-bit Break Character Transmit

Auto-Baud Rate Detection

The receiver block diagram is shown in below Figure. The data is received on the RB4/AN6/RX/DT/KBI0 pin and drives the data recovery block. The data recovery block is actually a high-speed shifter when break pic18f252 pic mcu flash memory, operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at FOSC. This mode would typically be used in RS-232 systems.

To set up an Asynchronous Reception:

- Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- If interrupts are desired, set enable bit RCIE.

- If 9-bit reception is desired, set bit RX9.

- Enable the reception by setting bit CREN.

- Flag bit, RCIF, will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register.

- If any error occurred, clear the error by clearing enable bit CREN.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.