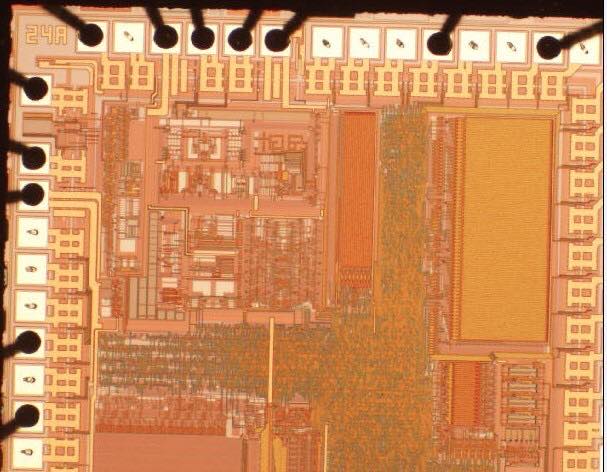

Decrypt Renesas MCU R5F52318ADFP#30 Flash Memory

Decrypt Renesas MCU R5F52318ADFP#30 Flash Memory and recover embedded firmware from microcontroller flash memory then copy binary to new microprocessor;

- CPU CPU

- · Maximum operating frequency: 32 MHz

- 32-bit RX CPU

- Minimum instruction execution time: One instruction per clock cycle

- Address space: 4-Gbyte linear

- Register set

General purpose: Sixteen 32-bit registers Control: Eight 32-bit registers Accumulator: One 64-bit register

- Basic instructions: 73

- DSP instructions: 9

- Addressing modes: 10

- Data arrangement Instructions: Little endian

Data: Selectable as little endian or big endian

- On-chip 32-bit multiplier: 32-bit × 32-bit → 64-bit

- On-chip divider: 32-bit ÷ 32-bit → 32 bits

Barrel shifter: 32 bits

Memory ROM · Capacity: 16 K /32 K /64 K /96 K /128 K /256 K /384 K /512 Kbytes

- 32 MHz, no-wait memory access

- Programming/erasing method:

Serial programming (asynchronous serial communication/USB communication), self-programming

RAM · Capacity: 8 K /10 K /16 K /32 K /64 Kbytes

32 MHz, no-wait memory access

E2 DataFlash · Capacity: 8 Kbytes

Number of erase/write cycles: 1,000,000 (typ)

Clock Clock generation circuit · Main clock oscillator, sub-clock oscillator, low-speed on-chip oscillator, high-speed on-chip oscillator,

PLL frequency synthesizer, and IWDT-dedicated on-chip oscillator

- Oscillation stop detection: Available

- Clock frequency accuracy measurement circuit (CAC)

- Independent settings for the system clock (ICLK), peripheral module clock (PCLK), and FlashIF clock (FCLK)

The CPU and system sections such as other bus masters run in synchronization with the system clock (ICLK): 32 MHz (at max.) to facilitate the process of crack renesas microcontroller r5f563nf flash memory;

Peripheral modules run in synchronization with the PCLK: 32 MHz (at max.)

The flash peripheral circuit runs in synchronization with the FCLK: 32 MHz (at max.

The ICLK frequency can only be set to FCLK, PCLKB, or PCLKD multiplied by n (n: 1, 2, 4, 8, 16, 32, 64).

Resets RES# pin reset, power-on reset, voltage monitoring reset, independent watchdog timer reset, and software reset to facilitate the process of CPLD XC9572 jed file decryption