Crack Protected MC68HC08AZ60 Memory

Crack Protected MC68HC08AZ60 Memory needs to understand the features of this Microcontroller,

The M68HC08 CPU (central processor unit) is an enhanced and fully object-code-compatible version of the M68HC05 CPU. The CPU08 Reference Manual (Freescale document order number CPU08RM/AD) contains a description of the CPU instruction set, addressing modes, and architecture.

• Object code fully upward-compatible with M68HC05 Family

• 16-bit stack pointer with stack manipulation instructions

• 16-bit index register with x-register manipulation instructions

• 8-MHz CPU internal bus frequency

• 64K-byte program/data memory space

• 16 addressing modes

• Memory-to-memory data moves without using accumulator

• Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

• Enhanced binary-coded decimal (BCD) data handling

• Modular architecture with expandable internal bus definition for extension of addressing range beyond 64K-bytes

• Low-power stop and wait modes

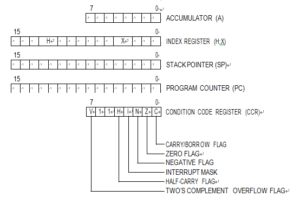

Below Figure shows the five CPU registers. CPU registers are not part of the memory map.

The accumulator is a general-purpose 8-bit register. The CPU uses the accumulator to hold operands and the results of arithmetic/logic operations similar to Crack MCU MC68HC908JL3 Flash Binary.

The 16-bit index register allows indexed addressing of a 64K-byte memory space. H is the upper byte of the index register, and X is the lower byte. H:X is the concatenated 16-bit index register.

In the indexed addressing modes, the CPU uses the contents of the index register to determine the conditional address of the operand. The index register can serve also as a temporary data storage location to recover MCU.