Crack NXP P89C592 MCU Program Memory

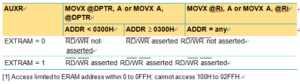

Crack NXP P89C592 MCU Program Memory can start from the eeprom reading, When EXTRAM = 1, MOVX @Ri and MOVX @DPTR will be similar to the standard 8051. Using MOVX @Ri provides an 8-bit address with multiplexed data on Port 0. Other output port pins can be used to output higher order address bits.

This provides external paging and MCU copying capabilities . Using MOVX @DPTR generates a 16-bit address. This allows external addressing up the 64 kB. Port 2 provides the high-order eight address bits (DPH), and Port 0 multiplexes the low order eight address bits (DPL) with data.

Both MOVX @Ri and MOVX @DPTR generates the necessary read and write signals (P3.6 – WR and P3.7 – RD) for external memory use.

Below Table shows external data memory RD, WR operation with EXTRAM bit.

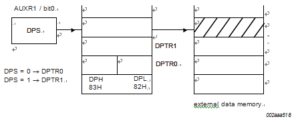

The stack pointer (SP) can be located anywhere within the 256 bytes of internal RAM (lower 128 bytes and upper 128 bytes). The stack pointer may not be located in any part of the expanded RAM only when Dump NXP P89V52X2 Embedded Firmware. The device has two 16-bit data pointers. The DPTR Select (DPS) bit in AUXR1 determines which of the two data pointers is accessed. When DPS = 0, DPTR0 is selected; when DPS = 1, DPTR1 is selected.

Quickly switching between the two data pointers can be accomplished by a single INC instruction on AUXR1 (see below Figure).