Crack NXP Microcontroller P89C838 Protected Firmware

Engineer need to understand the interrupt priority structure to get access to the databus of P89C838 which will makes Crack NXP Microcontroller P89C838 Protected Firmware becomes possible.

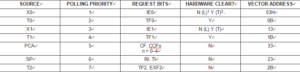

The P89C838 have a 7-source four-level interrupt structure (see below Table). The P89C838 only have a 6-source four-level interrupt structure because these devices do not have a PCA.

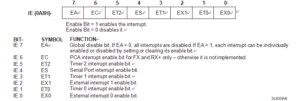

There are 3 SFRs associated with the four-level interrupt. They are the IE, IP, and IPH. (See below Figures) The IPH (Interrupt Priority High) register makes the four-level interrupt structure possible. The IPH is located at SFR address B7H. The structure of the IPH register and a description of its bits.

The function of the IPH SFR is simple and when combined with the IP SFR determines the priority of each interrupt after Crack NXP Microcontroller P89C838 Protected Firmware. The priority of each interrupt is determined as shown in the following table:

The priority scheme for servicing the interrupts is the same as that for the 80C51, except there are four interrupt levels rather than two as on the 80C51.

An interrupt will be serviced as long as an interrupt of equal or higher priority is not already being serviced. If an interrupt of equal or higher level priority is being serviced by NXP Microcontroller P89LPC931 Firmware Unlocking, the new interrupt will wait until it is finished before being serviced.

If a lower priority level interrupt is being serviced, it will be stopped and the new interrupt serviced. When the new interrupt is finished, the lower priority level interrupt that was stopped will be completed.