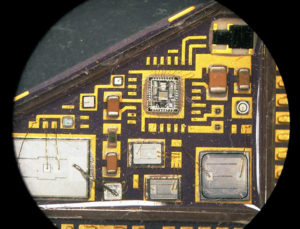

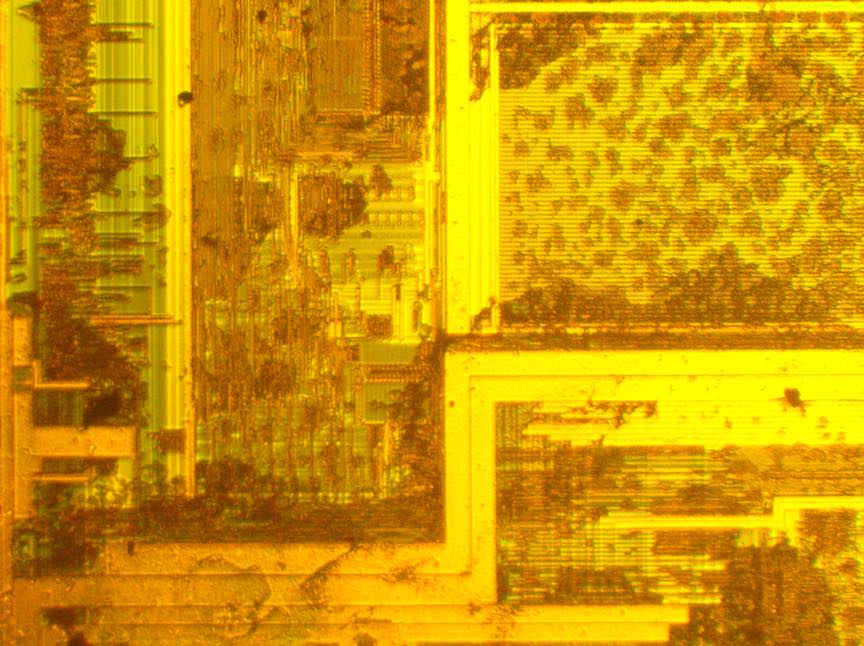

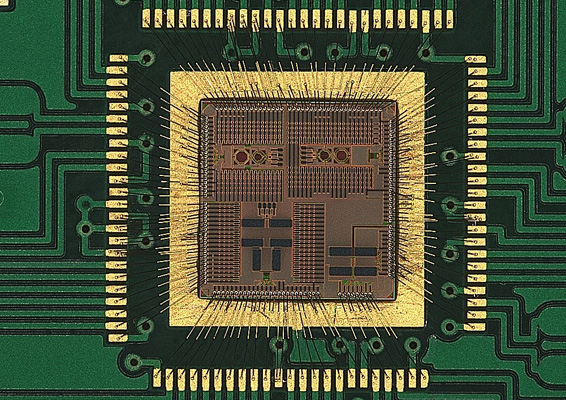

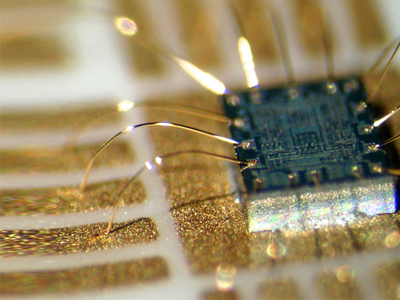

Crack Microcontroller PIC18F86K90 Binary

Crack Microcontroller PIC18F86K90 and extract IC Binary from embedded flash and eeprom memory, the fuse bit of MCU will be broken to disable the protection of microcontroller;

During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected.

Therefore, specific values of R1 and C1 will need to be adjusted based on the application and PCB requirements. For example, it is recommended that the capacitor, C1, be isolated from the MCLR pin during programming and debugging operations by using a jumper.

The jumper is replaced for normal run-time operations. Any components associated with the MCLR pin should be placed within 0.25 inch (6 mm) of the pin. The on-chip voltage regulator enable pin, ENVREG, must always be connected directly to either a supply voltage or to ground. Tying ENVREG to VDD enables the regulator, while tying it to ground disables the regulator before unlock pic18f4539 Microcontroller.

Refer to Section 28.3 “On-Chip Voltage Regulator” for details on connecting and using the on-chip regulator. When the regulator is enabled, a low-ESR (< 5Ω) capacitor is required on the VCAP/VDDCORE pin to stabilize the voltage regulator output voltage. The VCAP/VDDCORE pin must not be connected to VDD and must use a capacitor of 10 mF connected to ground.

The type can be ceramic or tantalum. A suitable example is the Murata GRM21BF50J106ZE01 (10 mF, 6.3V) or equivalent. Designers may use Figure 2-3 to evaluate ESR equivalence of candidate devices. It is recommended that the trace length not exceed 0.25 inch (6 mm). Refer to Section 31.0 “Electrical Characteristics” for additional information before read mcu pic18f4450 software.

When the regulator is disabled, a 0.1 mF capacitor should be connected from the VCAP/VDDCORE pin to ground. This capacitor’s characteristics must be similar to those of the “decoupling” capacitors explained in Section 2.2.1 “Decoupling Capacitors”. For details on the VDD requirement, when the regulator is disabled, see parameter D001 in Section 31.0 “Electrical Characteristics”.

Some PIC18FXXKXX families or some devices within a family do not provide the option of enabling or disabling the on-chip voltage regulator:

· Some devices (with the name, PIC18LFXXKXX) permanently disable the voltage regulator. These devices’ do not have the ENVREG pin and require a 0.1 mF capacitor on the VCAP/VDDCORE pin. The VDD level of these devices must comply with the “voltage regulator disabled” specification for parameter D001, in Section 31.0 “Electrical Characteristics”.

· Some devices permanently enable the voltage regulator. These devices also do not have the ENVREG pin. The 10mF capacitor is still required on the VCAP/VDDCORE pin. For details on all members of the PIC18F87K90 family, see Section 28.3 “On-Chip Voltage Regulator”.

Tags: crack microcontroller flash archive,crack microcontroller flash code,crack microcontroller flash content,crack microcontroller flash data,crack microcontroller flash eeprom,crack microcontroller flash file,crack microcontroller flash firmware,crack microcontroller flash information,crack microcontroller flash memory,crack microcontroller flash program