Crack Microcontroller PIC16C716 Heximal

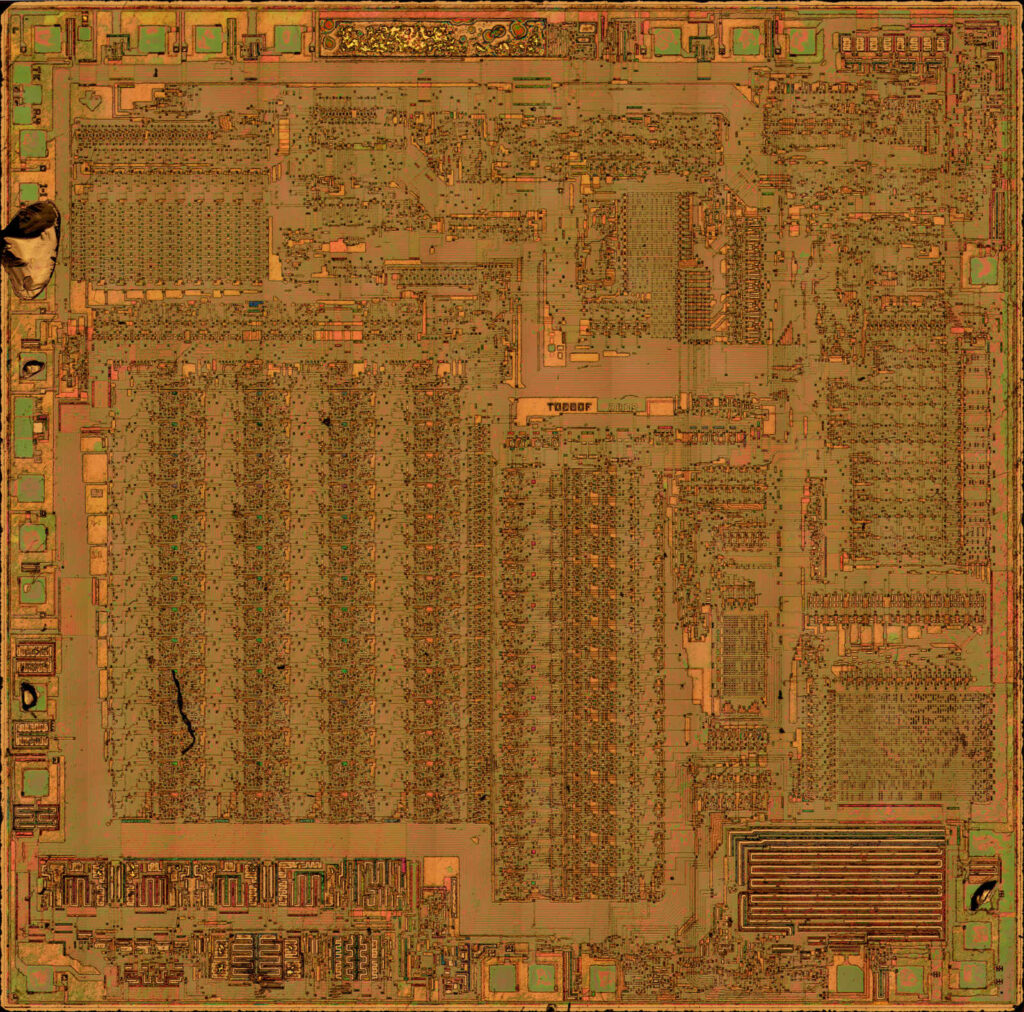

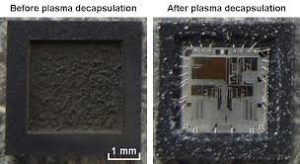

Crack Microcontroller PIC16C716 means the status of MCU PIC16C716 will be reset from locked to unlocked and Heximal content from flash memory will be extracted and copy to blank MCU;

Crack Microcontroller PIC16C716 means the status of MCU PIC16C716 will be reset from locked to unlocked and Heximal content from flash memory will be extracted and copy to blank MCU

There are two memory blocks in each of these PICmicro® microcontroller devices. Each block (Program Memory and Data Memory) has its own bus so that concurrent access can occur. Additional information on device memory may be found in the PICmicro Mid-Range Reference Manual, (DS33023).

The PIC16C712/716 has a 13-bit program counter capable of addressing an 8K x 14 program memory space. PIC16C712 has 1K x 14 words of program memory and PIC16C716 has 2K x 14 words of program memory. Accessing a location above the physically implemented address will cause a wraparound if extract mcu pic16f886 software.

The reset vector is at 0000h and the interrupt vector is at 0004h.

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special

Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain special function registers. Some “high use” special function registers from one bank may be mirrored in another bank for code reduction and quicker access.

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is give in Table 2-1 after Crack Microcontroller.

The special function registers can be classified into two sets; core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in that peripheral feature section after extract chip pic16f87 code.

The STATUS register, shown in Figure 2-4, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory. The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

The program counter (PC) specifies the address of the instruction to fetch for execution. The PC is 13 bits wide. The low byte is called the PCL register. This register is readable and writable. The high byte is called the PCH register. This register contains the PC<12:8> bits and is not directly readable or writable. All updates to the PCH register go through the PCLATH register.

The stack allows a combination of up to 8 program calls and interrupts to occur. The stack contains the return address from this branch in program execution. Midrange devices have an 8 level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution when Crack read Microcontroller pic16f71 bin.

PCLATH is not modified when the stack is PUSHed or POPed.

After the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

The CALL and GOTO instructions provide 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper bit of the address is provided by PCLATH<3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bit is programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is pushed onto the stack. Therefore, manipulation of the PCLATH<3> bit is not required for the return instructions (which POPs the address from the stack).

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000u u1uu (where u = unchanged).

Tags: crack microcontroller heximal archive,crack microcontroller heximal code,crack microcontroller heximal content,crack microcontroller heximal data,crack microcontroller heximal eeprom,crack microcontroller heximal file,crack microcontroller heximal firmware,crack microcontroller heximal information,crack microcontroller heximal memory,crack microcontroller heximal program