Crack Microcontroller P89C669 Eeprom Memory

As a very important joint to manipulate the center processor in P89C669, Crack Microcontroller P89C669 Eeprom Memory need to have some knowledge about the UART,

The UART operates in all of the usual modes that are described in the first section of Data Handbook IC20, 80C51-Based 8-Bit Microcontrollers. In addition the UART can perform framing error detect by looking for missing stop bits, and automatic address recognition. The UART also fully supports multiprocessor communication as does the standard 80C51 UART.

Crack Microcontroller P89C669 Eeprom Memory

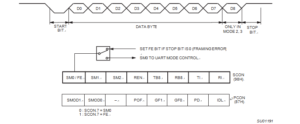

When used for framing error detect the UART looks for missing stop bits in the communication. A missing bit will set the FE bit in the SCON register. The FE bit shares the SCON.7 bit with SM0 and the function of SCON.7 is determined by PCON.6 (SMOD0). If SMOD0 is set then SCON.7 functions as FE. SCON.7 functions as SM0 when SMOD0 is cleared. When used as FE SCON.7 can only be cleared by software. Refer to below Figure.

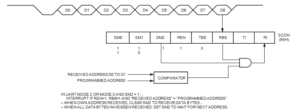

Automatic Address Recognition is a feature which allows the UART to recognize certain addresses in the serial bit stream by using hardware to make the comparisons when Crack Microcontroller P89C669 Eeprom Memory. This feature saves a great deal of software overhead by eliminating the need for the software to examine every serial address which passes by the serial port.

This feature is enabled by setting the SM2 bit in SCON. In the 9 bit UART modes, mode 2 and mode 3, the Receive Interrupt flag (RI) will be automatically set when the received byte contains either the “Given” address or the “Broadcast” address which can help to ease the process of NXP MCU P87C554 Embedded Firmware Unlocking.

The 9 bit mode requires that the 9th information bit is a 1 to indicate that the received information is an address and not data. Automatic address recognition is shown in below Figure.

The 8 bit mode is called Mode 1. In this mode the RI flag will be set if SM2 is enabled and the information received has a valid stop bit following the 8 address bits and the information is either a Given or Broadcast address. Mode 0 is the Shift Register mode and SM2 is ignored.