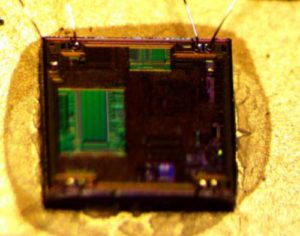

Crack Microcontroller Microchip PIC18F8722

We can Crack Microcontroller Microchip PIC18F8722, please view below IC Chip features for your reference:

Power-Managed Modes:

Peripheral Highlights (Continued):

Idle: CPU off, peripherals on

Sleep: CPU off, peripherals off

Idle mode currents down to 15 µA typical

Sleep current down to 0.2 µA typical

Timer1 Oscillator: 1.8 µA, 32 kHz, 2V

Watchdog Timer: 2.1 µA

Two-Speed Oscillator Start-up

· Three Enhanced Capture/Compare/PWM (ECCP) modules:

– One, two or four PWM outputs

– Selectable polarity

– Programmable dead-time

– Auto-Shutdown and Auto-Restart

· Two Master Synchronous Serial Port (MSSP) modules supporting 2/3/4-wire SPI™ (all 4 modes) and I2C™ Master and Slave modes

Flexible Oscillator Structure:

· Four Crystal modes, up to 25 MHz

· 4X Phase Lock Loop (PLL) (available for crystal and

internal oscillators)

· Two External RC modes, up to 4 MHz

· Two External Clock modes, up to 40 MHz

· Internal oscillator block:

– 8 user selectable frequencies, from 31 kHz to 8 MHz

– Provides a complete range of clock speeds from 31 kHz to 32 MHz when used with PLL

– User tunable to compensate for frequency drift

· Secondary oscillator using Timer1 @ 32 kHz

· Fail-Safe Clock Monitor:

– Allows for safe shutdown if peripheral clock stops

External Memory Interface

(PIC18F8627/8722 only):

· Address capability of up to 2 Mbytes

· 8-bit or 16-bit interface

Peripheral Highlights:

· Two Enhanced Addressable USART modules:

– Supports RS-485, RS-232 and LIN 1.2

– RS-232 operation using internal oscillator block (no external crystal required)

– Auto-wake-up on Start bit from Crack Microcontroller Microchip PIC18F8722

– Auto-baud detect

· 10-bit, up to 16-channel Analog-to-Digital Converter module (A/D)

– Auto-acquisition capability

– Conversion available during Sleep

· Dual analog comparators with input multiplexing

Special Microcontroller Features:

· C compiler optimized architecture:

– Optional extended instruction set designed to optimize re-entrant code

· 100,000 erase/write cycle Enhanced Flash program memory typical

· 1,000,000 erase/write cycle Data EEPROM memory typical

· Flash/Data EEPROM Retention: 100 years typical

High current sink/source 25 mA/25 mA

Four programmable external interrupts

Four input change interrupts

Two Capture/Compare/PWM (CCP) modules

· Priority levels for interrupts

· 8 X 8 Single Cycle Hardware Multiplier

· Extended Watchdog Timer (WDT):

– Programmable period from 4 ms to 131s

· Single-supply In-Circuit Serial Programming™ (ICSP™) via two pins

· In-Circuit Debug (ICD) via two pins

· Wide operating voltage range: 2.0V to 5.5V