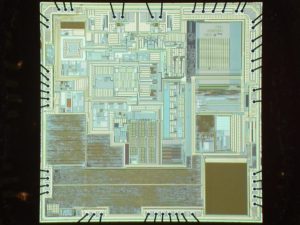

Crack MCU PIC18F8621 Heximal

Crack MCU PIC18F8621 flash and eeprom memory, recover Heximal and download the firmware to other blank Microcontroller to provide the same functions;

The EC, ECIO, EC+PLL and EC+SPLL Oscillator modes require an external clock source to be connected to the OSC1 pin. The feedback device between OSC1 and OSC2 is turned off in these modes to save current. There is a maximum 1.5 µs start-up required after a Power-on Reset or wake-up from Sleep mode.

In the EC Oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic. Figure 2-4 shows the pin connections for the EC Oscillator mode.

The ECIO Oscillator mode functions like the EC mode except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6). Figure 2-5 shows the pin connections for the ECIO Oscillator mode.

A Phase Locked Loop circuit is provided as a programmable option for users that want to multiply the frequency of the incoming oscillator signal by 4. For an input clock frequency of 10 MHz, the internal clock frequency will be multiplied to 40 MHz. This is useful for customers who are concerned with EMI due to high-frequency crystals.

The PLL can only be enabled when the oscillator configuration bits are programmed for High-Speed Oscillator or External Clock mode. If they are programmed for any other mode, the PLL is not enabled and the system clock will come directly from OSC1. There are two types of PLL modes: Software Controlled PLL and Configuration Bits Controlled PLL.

In Software Controlled PLL mode, PIC18F8621 executes at regular clock frequency after all Reset conditions. During execution, the application can enable PLL and switch to 4x clock frequency operation by setting the PLLEN bit in the OSCCON register. In Configuration Bits Controlled PLL, the PLL operation cannot be changed “on-the-fly”.

To enable or disable it, the controller must either cycle through a Power-on Reset, or switch the clock source from the main oscillator to the Timer1 oscillator and back again in order to finalize the process of IC code extraction;

The type of PLL is selected by programming FOSC<3:0> configuration bits in the CONFIG1H Configuration register. The oscillator mode is specified during device programming. A PLL lock timer is used to ensure that the PLL has locked before device execution starts. The PLL lock timer has a time-out that is called TPLL.

The PIC18F8621 devices include a feature that allows the system clock source to be switched from the main oscillator to an alternate low frequency clock source. For the PIC18F6525/6621/8525/8621 devices, this alternate clock source is the Timer1 oscillator. If a low-frequency crystal (32 kHz, for example) has been attached to the Timer1 oscillator pins and the Timer1 oscillator has been enabled, the device can switch to a low-power execution mode.

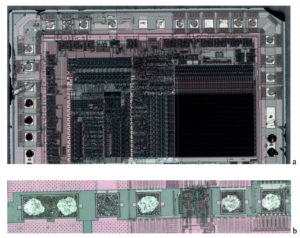

Figure 2-7 shows a block diagram of the system clock sources. The clock switching feature is enabled by programming the Oscillator Switching Enable (OSCSEN) bit in the CONFIG1H Configuration register to a ‘0’. Clock switching is disabled in an erased device.

Tags: crack mcu dump archive,crack mcu dump code,crack mcu dump content,crack mcu dump data,crack mcu dump eeprom,crack mcu dump file,crack mcu dump firmware,crack mcu dump information,crack mcu dump memory,crack mcu dump program