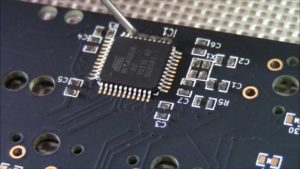

Crack MCU PIC16F720 Binary

Crack MCU PIC16F720 Binary or heximal from memory, extract the firmware from flash and eeprom, and copy the code to blank Microcontroller;

The PIC16F720/LF720 has a 13-bit program counter capable of addressing a 2K x 14 program memory space (0000h-07FFh), a 4K x 14 program memory space for the PIC16F721/LF721 (0000h-0FFFh). Accessing a location above the memory boundaries for the PIC16F720/LF720 will cause a wrap-around within the first 2K x 14 program memory space.

Accessing a location above the memory boundaries for the PIC16F721/LF721 will cause a wrap-around within the first 4K x 14 program memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h.

The data memory is partitioned into multiple banks which contain the General Purpose Registers (GPRs) and the Special Function Registers (SFRs). Bits RP0 and RP1 are bank select bits. Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers.

Above the Special Function Registers are the General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some frequently used Special Function Registers from one bank are mirrored in another bank for code reduction and quicker access.

The on-chip POR circuit holds the chip in Reset until VDD has reached a high enough level for proper operation. A maximum rise time for VDD is required. See Section 23.0 “Electrical Specifications” for details. If the BOR is enabled, the maximum rise time specification does not apply. The BOR circuitry will keep the device in Reset until VDD reaches VBOR (see Section 3.5 “Brown-Out Reset (BOR)”).

When the device starts normal operation (exits the Reset condition), device operating parameters (i.e., voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

For additional information, refer to Application Note AN607, “Power-up Trouble Shooting” (DS00607). Brown-out Reset is enabled by programming the BOREN<1:0> bits in the Configuration register. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

Two bits are used to enable the BOR. When BOREN = 11, the BOR is always enabled. When BOREN = 10, the BOR is enabled, but disabled during Sleep. When BOREN = 0X, the BOR is disabled. If VDD falls below VBOR for greater than parameter (TBOR) (see Section 23.0 “Electrical Specifications”), the Brown-out situation will reset the device.

This will occur regardless of VDD slew rate. A Reset is not ensured to occur if VDD falls below VBOR for more than parameter (TBOR). If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOR, the Power-up Timer will execute a 64 ms Reset.

On power-up, the time-out sequence is as follows: first, PWRT time-out is invoked after POR has expired, then OST is activated after the PWRT time-out has expired. The total time-out will vary based on oscillator configuration and PWRTE bit status. For example, in EC mode with PWRTE bit = 1 (PWRT disabled), there will be no time-out at all. Figure 3-4, Figure 3-5 and Figure 3-6 depict time-out sequences.

Since the time-outs occur from the POR pulse, if MCLR is kept low long enough, the time-outs will expire. Then, bringing MCLR high will begin execution immediately (see Figure 3-5). This is useful for testing purposes or to synchronize more than one PIC16F/LF720/721 device operating in parallel. Table 3-5 shows the Reset conditions for some special registers.

Tags: crack mcu embedded archive,crack mcu embedded code,crack mcu embedded content,crack mcu embedded data,crack mcu embedded eeprom,crack mcu embedded file,crack mcu embedded firmware,crack mcu embedded information,crack mcu embedded memory,crack mcu embedded program