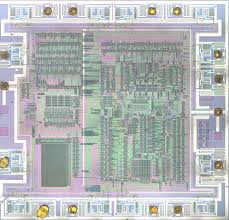

Crack MCU dsPIC30F5013 Firmware

Crack MCU dsPIC30F5013 Firmware is the process to extract the data and program from flash and eeprom, then copy the content from blank Microcontroller to provide the same functions;

The 17 x 17-bit multiplier is capable of signed or unsigned operation and can multiplex its output using a scaler to support either 1.31 fractional (Q31) or 32-bit integer results. Unsigned operands are zero-extended into the 17th bit of the multiplier input value.

Signed operands are sign-extended into the 17th bit of the multiplier input value. The output of the 17 x 17-bit multiplier/scaler is a 33-bit value which is sign-extended to 40 bits. Integer data is inherently represented as a signed two’s complement value, where the MSB is defined as a sign bit. Generally speaking, the range of an N-bit two’s complement integer is -2N-1 to 2N-1 – 1.

For a 16-bit integer, the data range is -32768 (0x8000) to 32767 (0x7FFF) including ‘0’. For a 32-bit integer, the data range is -2,147,483,648 (0x8000 0000) to 2,147,483,645 (0x7FFF FFFF). When the multiplier is configured for fractional multiplication, the data is represented as a two’s complement fraction, where the MSB is defined as a sign bit and the radix point is implied to lie just after the sign bit (QX format).

The range of an N-bit two’s complement fraction with this implied radix point is -1.0 to (1 – 21-N). For a 16-bit fraction, the Q15 data range is -1.0 (0x8000) to 0.999969482 (0x7FFF) including ‘0’ and has a precision of 3.01518×10-5. In Fractional mode, the 16×16 multiply operation generates a 1.31 product which has a precision of 4.65661 x 10-10.

The same multiplier is used to support the MCU multiply instructions which include integer 16-bit signed, unsigned and mixed sign multiplies to support the process of IC code extraction. The MUL instruction may be directed to use byte or word sized operands. Byte operands will direct a 16-bit result, and word operands will direct a 32-bit result to the specified register(s) in the W array.

The data accumulator consists of a 40-bit adder/subtracter with automatic sign extension logic. It can select one of two accumulators (A or B) as its preaccumulation source and post-accumulation destination. For the ADD and LAC instructions, the data to be accumulated or loaded can be optionally scaled via the barrel shifter, prior to accumulation.

The OA and OB bits are modified each time data passes through the adder/subtracter. When set, they indicate that the most recent operation has overflowed into the accumulator guard bits (bits 32 through 39). The OA and OB bits can also optionally generate an arithmetic warning trap when set and the corresponding overflow trap flag enable bit (OVATE, OVBTE) in the INTCON1 register (refer to Section 5.0 “Interrupts”) is set. This allows the user to take immediate action, for example, to correct system gain.

The SA and SB bits are modified each time data passes through the adder/subtracter but can only be cleared by the user. When set, they indicate that the accumulator has overflowed its maximum range (bit 31 for 32-bit saturation, or bit 39 for 40-bit saturation) and will be saturated (if saturation is enabled). When saturation is not enabled, SA and SB default to bit 39 over-flow and thus indicate that a catastrophic overflow has occurred. If the COVTE bit in the INTCON1 register is set, SA and SB bits will generate an arithmetic warning trap when saturation is disabled.

The overflow and saturation status bits can optionally be viewed in the STATUS register (SR) as the logical OR of OA and OB (in bit OAB) and the logical OR of SA and SB (in bit SAB). This allows programmers to check one bit in the STATUS register to determine if either accumulator has overflowed, or one bit to determine if either accumulator has saturated.

This would be useful for complex number arithmetic which typically uses both the accumulators. Bit 39 Overflow and Saturation: When bit 39 overflow and saturation occurs, the saturation logic loads the maximally positive 9.31 (0x7FFFFFFFFF), or maximally negative 9.31 value (0x8000000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user. This is referred to as ‘super saturation’ and provides protection against erroneous data, or unexpected algorithm problems (e.g., gain calculations).

Bit 31 Overflow and Saturation: When bit 31 overflow and saturation occurs, the saturation logic then loads the maximally positive 1.31 value (0x007FFFFFFF), or maximally negative 1.31 value (0x0080000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user. When this Saturation mode is in effect, the guard bits are not used (so the OA, OB or OAB bits are never set).

Tags: crack mcu heximal archive,crack mcu heximal code,crack mcu heximal content,crack mcu heximal data,crack mcu heximal eeprom,crack mcu heximal file,crack mcu heximal firmware,crack mcu heximal information,crack mcu heximal memory,crack mcu heximal program