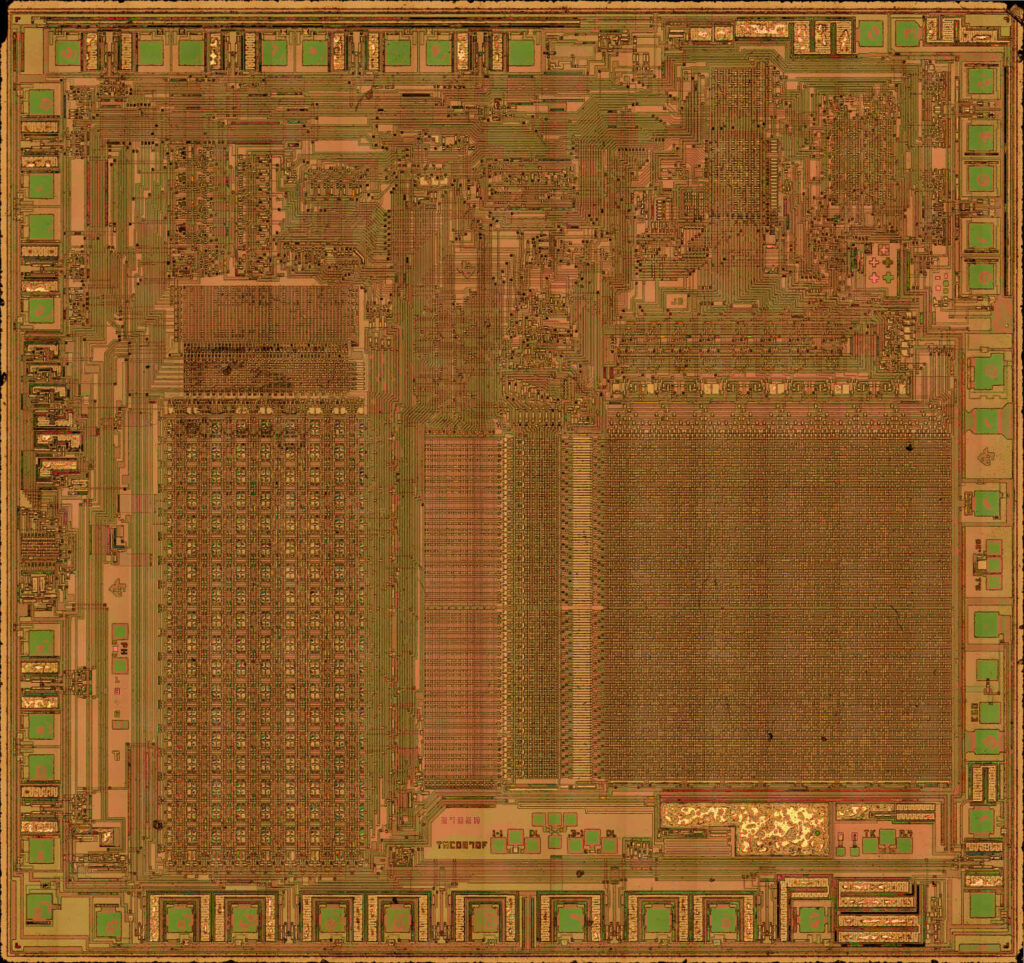

Crack IC ATmega169PV Flash

Crack IC ATmega169PV Flash and recover the locked heximal from mcu atmega169pv flash memory, copy firmware content to new mcu atmega169pv memory;

Instructions that use indirect addressing access the upper 128 bytes of RAM. For example, the following indirect addressing instruction, where R0 contains 0A0H, accesses the data byte at address 0A0H, rather than P2 (whose address is 0A0H).

MOV @R0, #data Note that stack operations are examples of indirect addressing, so the upper 128 bytes of data RAM are available as stack space if unlock mcu atmega644 firmware.

The programmable Watchdog Timer (WDT) operates from an independent oscillator. The prescaler bits, PS0, PS1 and PS2 in SFR WCON are used to set the period of the Watchdog Timer from 16 ms to 2048 ms.

The available timer periods are shown in the following table and the actual timer periods (at VCC = 5V) are within ±30% of the nominal. The WDT is disabled by Power-on Reset and during Power Down.

It is enabled by setting the WDTEN bit in SFR WCON (address = 96H). The WDT is reset by setting the WDTRST bit in WCON. When the WDT times out without being reset or disabled, an internal RST pulse is generated to reset the CPU before crack ic atmega644pa program.

Timer 0 and Timer 1 in the ATMEGA169PV operate the same way as Timer 0 and Timer 1 in the ATMEGA169PV. For further information, see the October 1995 Microcontroller Data Book, page 2-45, section titled, “Timer/Counters.”.

Timer 2 is a 16 bit Timer/Counter that can operate as either a timer or an event counter. The type of operation is selected by bit C/T2 in the SFR T2CON (shown in Table 2). Timer 2 has three operating modes: capture, auto-reload (up or down counting), and baud rate generator.

The modes are selected by bits in T2CON, as shown in Table 8. Timer 2 consists of two 8-bit registers, TH2 and TL2. In the Timer function, the TL2 register is incremented every machine cycle. Since a machine cycle consists of 12 oscillator periods, the count rate is 1/12 of the oscillator frequency.

Tags: crack ic archive,crack ic code,crack ic content,crack ic data,crack ic eeprom,crack ic file,crack ic firmware,crack ic information,crack ic memory,crack ic program