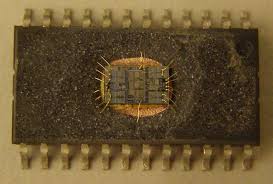

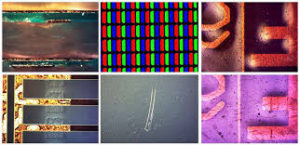

Crack Chip dsPIC30F6013A Flash

Crack Chip dsPIC30F6013A Flash memory and eeprom memory, extract the program and data out and clone the Microcontroller dsPIC30F6013A with the same functions;

The dsPIC DSC devices feature a 16/16-bit signed fractional divide operation, as well as 32/16-bit and 16/16-bit signed and unsigned integer divide operations, in the form of single instruction iterative divides. The following instructions and data sizes are supported:

DIVF – 16/16 signed fractional divide

DIV.sd – 32/16 signed divide

DIV.ud – 32/16 unsigned divide

DIV.sw – 16/16 signed divide

5. DIV.uw – 16/16 unsigned divide

The 16/16 divides are similar to the 32/16 (same number of iterations), but the dividend is either zero-extended or sign-extended during the first iteration. The DSP engine consists of a high-speed 17-bit x 17-bit multiplier, a barrel shifter and a 40-bit adder/subtracter (with two target accumulators, round and various bits in the CPU Core Configuration register (CORCON), as listed below:

1. Fractional or integer DSP multiply (IF). saturation logic).

The dsPIC30F is a single-cycle instruction flow architecture, therefore, concurrent operation of the DSP engine with MCU instruction flow is not possible. However, some MCU ALU and DSP engine resources may be used concurrently by the same instruction (e.g., ED, EDAC).

The DSP engine also has the capability to perform Signed or unsigned DSP multiply (US). Conventional or convergent rounding (RND).

Automatic saturation on/off for AccA (SATA).

Automatic saturation on/off for AccB (SATB).

Automatic saturation on/off for writes to data memory (SATDW).

Accumulator Saturation mode selection (ACCSAT).

inherent accumulator-to-accumulator operations, which require no additional data. These instructions are

For CORCON layout, see Table 3-3. ADD, SUB and NEG.

The 17 x 17-bit multiplier is capable of signed or unsigned operation and can multiplex its output using a scaler to support either 1.31 fractional (Q31) or 32-bit integer results. Unsigned operands are zero-extended into the 17th bit of the multiplier input value.

Signed operands are sign-extended into the 17th bit of the multiplier input value. The output of the 17 x 17-bit multiplier/scaler is a 33-bit value which is sign-extended to 40 bits. Integer data is inherently represented as a signed two’s complement value, where the MSB is defined as a sign bit before Crack Chip.

Generally speaking, the range of an N-bit two’s complement integer is -2N-1 to 2N-1 – 1. For a 16-bit integer, the data range is -32768 (0x8000) to 32767 (0x7FFF) including ‘0’. For a 32-bit integer, the data range is -2,147,483,648 (0x8000 0000) to 2,147,483,647 (0x7FFF FFFF).

When the multiplier is configured for fractional multiplication, the data is represented as a two’s complement fraction, where the MSB is defined as a sign bit and the radix point is implied to lie just after the sign bit (QX format). The range of an N-bit two’s complement fraction with this implied radix point is -1.0 to (1 – 21-N).

For a 16-bit fraction, the Q15 data range is -1.0 (0x8000) to 0.999969482 (0x7FFF) including ‘0’ and has a precision of 3.01518×10-5. In Fractional mode, the 16×16 multiply operation generates a 1.31 product which has a precision of 4.65661 x 10-10.

The same multiplier is used to support the MCU multiply instructions which include integer 16-bit signed, unsigned and mixed sign multiplies. The MUL instruction may be directed to use byte or word sized operands. Byte operands will direct a 16-bit result, and word operands will direct a 32-bit result to the specified register(s) in the W array.

Tags: crack chip embedded archive,crack chip embedded code,crack chip embedded content,crack chip embedded data,crack chip embedded eeprom,crack chip embedded file,crack chip embedded firmware,crack chip embedded information,crack chip embedded memory,crack chip embedded program