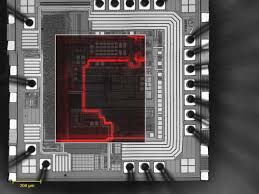

Crack Chip AT89C51RE2 Flash

Crack Chip AT89C51RE2 Flash memory, copy microcontroller embedded binary of at89c51re2 from flash and eeprom, the firmware of mcu at89c51re2 will be read after unlocking;

The upper 7 bits are the address to which the TWI module will respond when addressed by a master. If the LSB (GC) is set the TWI module will respond to the general call address (00h); otherwise it ignores the general call address. CR0, CR1 and CR2 have no effect in the slave mode. SSIE must be set to enable the TWI. The AA bit must be set to enable the own slave address or the general call address acknowledgement. STA, STO and SI must be cleared when Clone microchip mcu pic16f627a.

When SSADR and SSCON have been initialised, the TWI module waits until it is addressed by its own slave address followed by the data direction bit which must be at logic 0 (W) for the TWI to operate in the slave receiver mode. After its own slave address and the W bit have been received, the serial interrupt flag is set and a valid status code can be read from SSCS. This status code is used to vector to an interrupt service routine.The appropriate action to be taken for each of these status code is detailed in Table.

The slave receiver mode may also be entered if arbitration is lost while TWI is in the master mode (states 68h and 78h). If the AA bit is reset during a transfer, TWI module will return a not acknowledge (logic 1) to SDA after the next received data byte. While AA is reset, the TWI module does not respond to its own slave address. However, the 2-wire bus is still monitored and address recognition may be resume at any time by setting AA before decrypt microchip mcu pic16f648a memory.

This means that the AA bit may be used to temporarily isolate the module from the 2-wire bus. In the slave transmitter mode, a number of data bytes are transmitted to a master receiver (Figure 55). Data transfer is initialized as in the slave receiver mode. When SSADR and SSCON have been initialized, the TWI module waits until it is addressed by its own slave address followed by the data direction bit which must be at logic 1 (R) for TWI to operate in the slave transmitter mode. After its own slave address and the R bit have been received, the serial interrupt flag is set and a valid status code can be read from SSCS.

This status code is used to vector to an interrupt service routine. The appropriate action to be taken for each of these status code is detailed in Table . The slave transmitter mode may also be entered if arbitration is lost while the TWI module is in the master mode if decode mcu pic16f873 archieve.

If the AA bit is reset during a transfer, the TWI module will transmit the last byte of the transfer and enter state C0h or C8h. the TWI module is switched to the not addressed slave mode and will ignore the master receiver if it continues the transfer. Thus the master receiver receives all 1’s as serial data. While AA is reset, the TWI module does not respond to its own slave address.

However, the 2-wire bus is still monitored and address recognition may be resume at any time by setting AA. This means that the AA bit may be used to temporarily isolate the TWI module from the 2-wire bus. There are two SSCS codes that do not correspond to a define TWI hardware state (Table 106 ). These codes are discuss hereafter before unlock microchip mcu pic16f876 binary.

Status F8h indicates that no relevant information is available because the serial interrupt flag is not set yet. This occurs between other states and when the TWI module is not involved in a serial transfer. Status 00h indicates that a bus error has occurred during a TWI serial transfer. A bus error is caused when a START or a STOP condition occurs at an illegal position in the format frame. Examples of such illegal positions happen during the serial transfer of an address byte, a data byte, or an acknowledge bit. When a bus error occurs, SI is set. To recover from a bus error, the STO flag must be set and SI must be cleared. This causes the TWI module to enter the not addressed slave mode and to clear the STO flag (no other bits in SSCON are affected). The SDA and SCL lines are released and no STOP condition is transmitted.

Tags: és kinyerni a forráskódot a flash program memóriából és az eeprom adatmemóriából,és kivonja a forráskódot a flash program memóriából és az eeprom adatmemóriából,és vonja ki a forráskódot a flash program memóriából és az eeprom adatmemóriából,feltörni az AT89C51RE2 mikrokontroller biztosítékbitvédelmét,megszakítja az AT89C51RE2 mikrokontroller biztosíték bitvédelmét és kivonja a forráskódot a flash program memóriából és az eeprom adatmemóriából,megtámadja az AT89C51RE2 mikrokontroller biztosítékbitvédelmét,oldja fel az AT89C51RE2 mikrokontroller biztosítékbitvédelmét