Crack ATMEGA645V Microprocessor Flash Memory

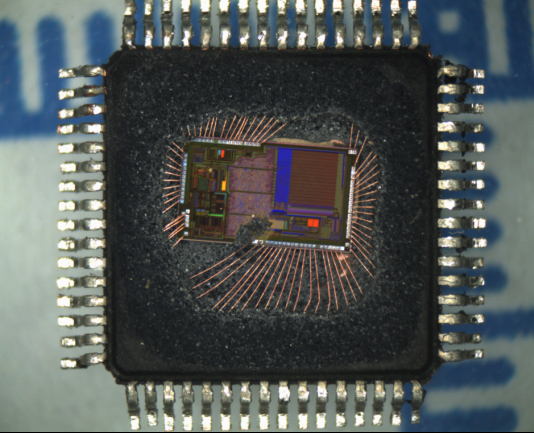

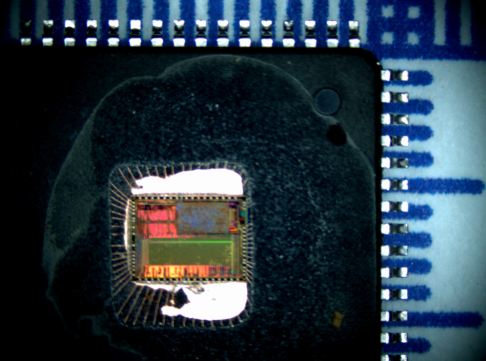

Crack ATMEGA645V Microprocessor Flash Memory security fuse bit, copy embedded firmware from atmega645v mcu flash and eeprom memory, the file format which can be readout from microcontroller atmega645v is heximal or binary;

It is possible to use the prescaler reset for synchronizing the Timer/Counter to program execution. However, care must be taken if the other Timer/Counter that shares the same prescaler also uses prescaling in the process of unlock atmega2561v microcontroller flash memory content. A prescaler reset will affect the prescaler period for all Timer/Counters it is connected to.

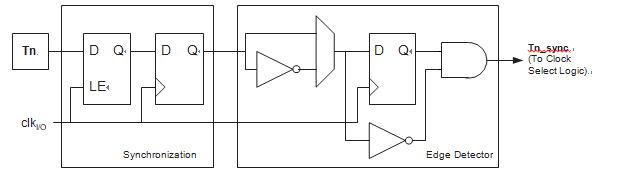

An external clock source applied to the T1/T0 pin can be used as Timer/Counter clock (clkT1/clkT0). The T1/T0 pin is sampled once every system clock cycle by the pin synchronization logic to crack atmega2561 mcu memory protection.

The synchronized (sampled) signal is then passed through the edge detector. Figure below shows a functional equivalent block diagram of the T1/T0 syn- chronization and edge detector logic. The registers are clocked at the positive edge of the internal system clock (clkI/O).

The latch is transparent in the high period of the internal system clock. The edge detector generates one clkT1/clkT0 pulse for each positive (CSn2:0 = 7) or negative (CSn2:0 = 6) edge it detects.

Tags: agrietarse archivo de software de microordenador protegido,agrietarse binario de memoria flash de chip MCU bloqueado,agrietarse código de firmware del microprocesador seguro,agrietarse programa heximal microcontrolador encriptado