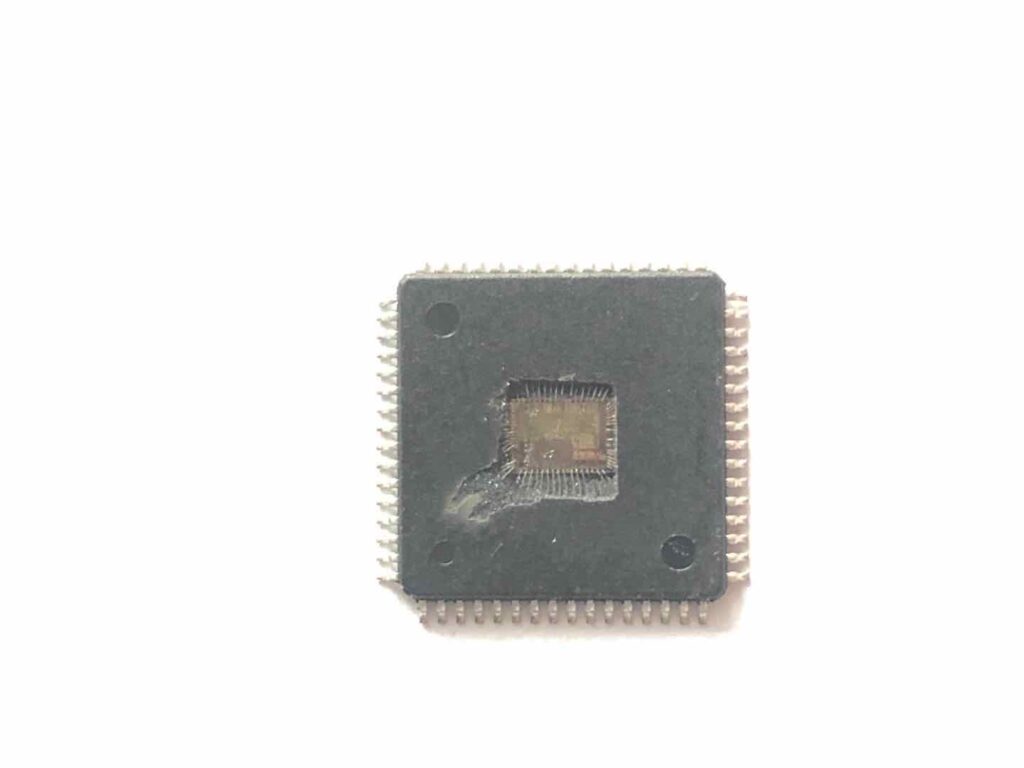

Crack Altera Eeprom PLD EPM7512BBC256-10 Fuse Bit

Crack Altera Eeprom PLD EPM7512BBC256-10 Fuse Bit and recover cpld epm7512bbc256 chipset protection system, and eeprom data inside cpld epm7512 cpld will be extracted;

The timing of WUE and RCIF events may cause some confusion when it comes to determining the validity of received data. As noted, setting the WUE bit places the EUSART in an Idle mode. The wake-up event causes a receive interrupt by setting the RCIF bit.

The WUE bit is cleared after this when a rising edge is seen on RX/ DT. The interrupt condition is then cleared by reading the RCREG register after attacking pld ic altera epm7128elc84 memory. Ordinarily, the data in RCREG will be dummy data and should be discarded.

The fact that the WUE bit has been cleared (or is still set) and the RCIF flag is set should not be used as an indicator of the integrity of the data in RCREG. Users should consider implementing a parallel method in firmware to verify received data integrity.

To assure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process to reverse pld ic altera epm7064lc44 memory. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

Tags: Altera Eeprom PLD EPM7512BBC256-10 Fuse Bit knacken und cpld epm7512bbc256 Chipsatz-Schutzsystem wiederherstellen und eeprom-Daten innerhalb von cpld epm7512 cpld werden extrahiert,Crack Altera Eeprom PLD EPM7512BBC256-10 Fuse Bit i odzyskaj cpld epm7512bbc256 system ochrony chipsetu i dane eeprom wewnątrz cpld epm7512 cpld zostaną wyodrębnione,Desbloquee Altera Eeprom PLD EPM7512BBC256-10 Fuse Bit y recupere el sistema de protección del chipset cpld epm7512bbc256 y se extraerán los datos eeprom dentro de cpld epm7512 cpld