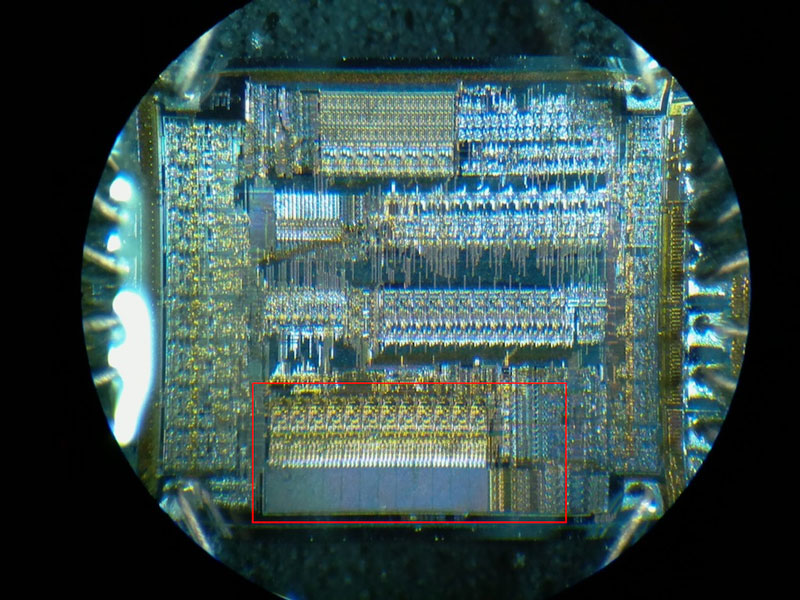

Copy Microcontroller PIC18F4620T Flash Heximal

Copy Microcontroller PIC18F4620T Flash Heximal after disable the protection fuse bit over MCU PIC18F4620T, readout program file from pic18f4620t;

When the BOREN bits of Configuration Words are programmed to ‘10’, the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold. BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

When the BOREN bits of Configuration Words are programmed to ‘01’, the BOR is controlled by the SBOREN bit. The device start-up is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit. BOR protection is unchanged by Sleep when read mcu ic pic18f4620 program out from its flash memory.

In this specific case, “Release of POR” and “Wake-up from Sleep”, there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

BOR is forced ON during PFM Bulk Erase operations to make sure that the system code protection cannot be compromised by reducing VDD. During Bulk Erase, the BOR is enabled at 2.45V, even if it is configured to some other value. If VDD falls, the erase cycle will be aborted, but the device will not be reset.