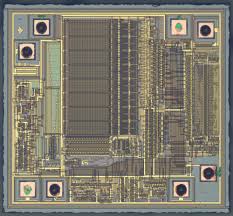

Copy Microcomputer IC Renasas HD64F3062B

Copy Microcomputer IC Renasas HD64F3062B

The H8/3062 Group is a series of microcontrollers (MCUs) that integrate system supporting functions together with an H8/300H CPU core having an original Renesas architecture which is important for Copy Microcomputer IC Renasas HD64F3062B.

The H8/300H CPU has a 32-bit internal architecture with sixteen 16-bit general registers, and a concise, optimized instruction set designed for speed. It can address a 16-Mbyte linear address space. Its instruction set is upward-compatible at the object-code level with the H8/300 CPU, enabling easy porting of software from the H8/300 Series.

The on-chip system supporting functions include ROM, RAM, a 16-bit timer, an 8-bit timer, a programmable timing pattern controller (TPC), a watchdog timer (WDT), a serial communication interface (SCI), an A/D converter, a D/A converter, I/O ports, and other facilities.

The 11 members of the H8/3062 Group are the H8/3062F-ZTAT R-mask version, H8/3062 (masked ROM version), H8/3061 (masked ROM version), H8/3060 (masked ROM version), H8/3064F-ZTAT B-mask version, H8/3062F-ZTAT B-mask version, H8/3064 masked ROM B-mask version, H8/3062 masked ROM B-mask version, H8/3061 masked ROM B-mask version, and H8/3060 masked ROM B-mask version.

Seven MCU operating modes offer a choice of bus width and address space size. The modes (modes 1 to 7) include two single-chip modes and five expanded modes.

In addition to its masked ROM versions, the H8/3062 Group has F-ZTAT™* versions with on-chip flash memory that allows programs to be freely rewritten by the user. This version enables users to respond quickly and flexibly to changing application specifications, growing production volumes, and other conditions.