Copy Freescale MC68HC908GR32 MCU Firmware

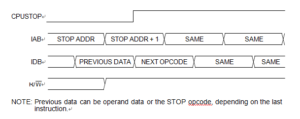

In stop mode, the SIM counter is reset by Copy Freescale MC68HC908GR32 MCU Firmware and the system clocks are disabled. An interrupt request from a module can cause an exit from stop mode. Stacking for interrupts begins after the selected stop recovery time has elapsed. Reset or break also causes an exit from stop mode.

The SIM disables the clock generator module outputs (CGMOUT and CGMXCLK) in stop mode, stopping the CPU and peripherals. Stop recovery time is selectable using the SSREC bit in the configuration register 1 (CONFIG1). If SSREC is set, stop recovery is reduced from the normal delay of 4096 CGMXCLK cycles down to 32 which can facilitate the process of Motorola MC68HC08AS20 MCU Flash Copying. This is ideal for applications using canned oscillators that do not require long start-up times from stop mode.

External crystal applications should use the full stop recovery time by clearing the SSREC bit.

A break interrupt during stop mode sets the SIM break STOP/WAIT bit (SBSW) in the SIM break status register (SBSR).

The SIM counter is held in reset from the execution of the STOP instruction until the beginning of stop recovery. It is then used to time the recovery period. Below Figure shows stop mode entry timing.

SBSW — SIM Break STOP/WAIT

This status bit is useful in applications requiring a return to stop or wait mode after exiting from a break interrupt. SBSW can be cleared by writing a logic 0 to it. Reset clears SBSW and Motorola MC68HC08AS32 Memory Program will be cloned.

1 = Stop or wait mode was exited by break interrupt

0 = Stop or wait mode was not exited by break interrupt

SBSW can be read within the break state SWI routine. The user can modify the return address on the stack by subtracting one from it to faciliate the MCU Reading. The following code is an example of this.

; This code works if the H register has been pushed onto the stack in the break

; service routine software. This code should be executed at the end of the

; break service routine software.

HIBYTE EQU 5

LOBYTE EQU 6

; If not SBSW, do RTI

BRCLR SBSW,SBSR, RETURN ;

;

See if STOP or WAIT mode was exited by break.

TST LOBYTE,SP ; If RETURNLO is not 0,

BNE DOLO ; then just decrement low byte. DEC HIBYTE,SP ; Else deal with high byte, too.

DOLO DEC LOBYTE,SP ; Point to STOP/WAIT opcode.

RETURN PULH

RTI

; Restore H register.