Clone NXP P89C660 Microcontroller Flash Program

The P89C660 have internal data memory that is mapped into four separate segments: the lower 128 bytes of RAM, upper 128 bytes of RAM, 128 bytes Special Function Register (SFR), and 256 bytes (768 for RD+) expanded RAM (EXTRAM). this features provides an effective way to Clone NXP P89C660 Microcontroller Flash Program.

The four segments are:

1. The Lower 128 bytes of RAM (addresses 00H to 7FH) are directly and indirectly addressable.

2. The Upper 128 bytes of RAM (addresses 80H to FFH) are indirectly addressable only.

3. The Special Function Registers, SFRs, (addresses 80H to FFH) are directly addressable only.

4. The 256-bytes (768 for RD+) expanded RAM ((EXTRAM (256-bytes) 00H–FFH)) and ((EXTRAM (768-bytes for RD+)

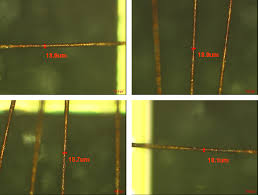

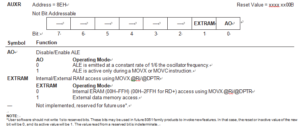

00H – 2FFH)) are indirectly accessed by move external instruction, MOVX, and with the EXTRAM bit cleared by Dump NXP P89V52X2 Embedded Firmware, see Below Figure.

The Lower 128 bytes can be accessed by either direct or indirect addressing. The Upper 128 bytes can be accessed by indirect addressing only. The Upper 128 bytes occupy the same address space as the SFR. That means they have the same address after Clone NXP P89C660 Microcontroller Flash Program, but are physically separate from SFR space.

When an instruction accesses an internal location above address 7FH, the CPU knows whether the access is to the upper 128 bytes of data RAM or to SFR space by the addressing mode used in the instruction. Instructions that use direct addressing access SFR space. For example:

MOV 0A0H,#data

accesses the SFR at location 0A0H (which is P2). Instructions that use indirect addressing access the Upper 128 bytes of data RAM.

For example:

MOV @R0,#data

where R0 contains 0A0H, accesses the data byte at address 0A0H, rather than P2 (whose address is 0A0H).

The EXTRAM can be accessed by indirect addressing, with EXTRAM bit cleared and MOVX instructions. This part of memory is physically located on-chip, logically occupies the first 256-bytes (768 for RD+) of external data memory.

With EXTRAM = 0, the EXTRAM is indirectly addressed, using the MOVX instruction in combination with any of the registers R0, R1 of the selected bank or DPTR. An access to EXTRAM will not affect ports P0, P3.6 (WR#) and P3.7 (RD#). P2 SFR is output during external addressing. For example, with EXTRAM = 0,

MOVX @R0,#data