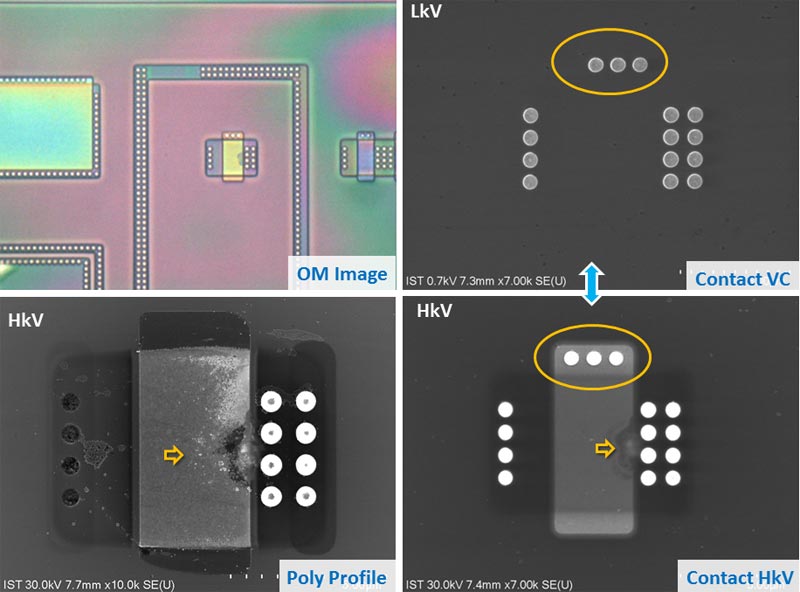

Clone Chip ATTINY48A Flash

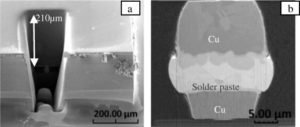

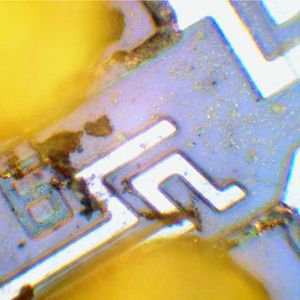

Clone Chip ATTINY48A Flash and eeprom memory content, the cloned file is heximal and extract out from embedded microcontroller ATtiny48A which will provide the same functions as original Microprocessor;

Clone Chip ATTINY48A Flash and eeprom memory content, the cloned file is heximal and extract out from embedded microcontroller ATtiny48A which will provide the same functions

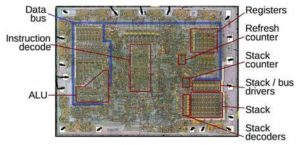

The AVR Stack Pointer is implemented as two 8-bit registers in the I/O space. The number of bits actually used is implementation dependent. Note that the data space in some implementations of the AVR architecture is so small that only SPL is needed.

In this case, the SPH Register will not be present. For ELPM/SPM instructions, the Z-pointer is a concatenation of RAMPZ, ZH, and ZL, as shown in Figure 7. Note that LPM is not affected by the RAMPZ setting if read chip pic16c770 eeprom.

The actual number of bits is implementation dependent. Unused bits in an implementation will always read as zero. For compatibility with future devices, be sure to write these bits to zero.

For EICALL/EIJMP instructions, the Indirect-pointer to the subroutine/routine is a concatenation of EIND, ZH, and ZL, as shown in Figure 8. Note that ICALL and IJMP are not affected by the EIND setting.

The actual number of bits is implementation dependent. Unused bits in an implementation will always read as zero. For compatibility with future devices, be sure to write these bits to zero when crack microcontroller pic16c716 heximal.

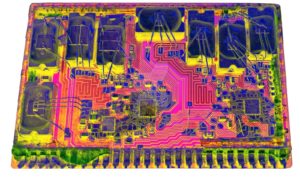

This section describes the general access timing concepts for instruction execution. The AVR CPU is driven by the CPU clock clkCPU, directly generated from the selected clock source for the chip. No internal clock division is used. Figure 9 shows the parallel instruction fetches and instruction executions enabled by the Harvard architecture and the fast-access Register File concept.

This is the basic pipelining concept to obtain up to 1 MIPS per MHz with the corresponding unique results for functions per cost, functions per clocks, and functions per power-unit after extract ic pic16c84 code.

The AVR provides several different interrupt sources. These interrupts and the separate Reset Vector each have a separate program vector in the program memory space.

All interrupts are assigned individual enable bits which must be written logic one together with the Global Interrupt Enable bit in the Status Register in order to enable the interrupt.

Depending on the Program Counter value, interrupts may be automatically disabled when Boot Lock bits BLB02 or BLB12 are programmed. This feature improves software security.

Tags: clone chip archive,clone chip bin,clone chip code,clone chip content,clone chip data,clone chip eeprom,clone chip file,clone chip firmware,clone chip hex,clone chip information,clone chip memory,clone chip program