Clone Altera EPM7064BLC44-7 PLD Eeprom Program

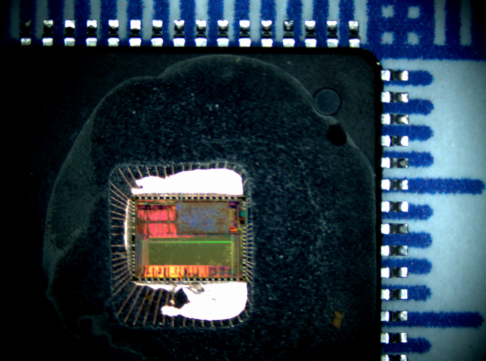

Clone Altera EPM7064BLC44-7 PLD Eeprom Program after breaking off the protection fuse bit over epm7064blc44 pld chip, the silicon package of epm7064blc44 pld will be decapsulated;

Following a wake-up event, the module generates an RCIF interrupt. The interrupt is generated synchro- nously to the Q clocks in normal operating modes and asynchronously if the device is in Sleep mode to clone altera epm7032vlc44 eeprom firmware, The interrupt condition is cleared by reading the RCREG register.

The WUE bit is automatically cleared once a low-to-high transition is observed on the RX line, following the wake- up event. At this point, the EUSART module is in Idle mode and returns to normal operation. This signals to the user that the Sync Break event is over.

Since auto-wake-up functions by sensing rising edge transitions on RX/DT, information with any state changes before the Stop bit may signal a false end-of-character.

and cause data or framing errors. To work properly, therefore, the initial character in the transmission must be all ‘0’s. This can be 00h (8 bytes) for standard RS-232 devices to copy pld epm7032blc44 eeprom pof file, or 000h (12 bits) for LIN bus. Oscillator start-up time must also be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL mode).

The Sync Break (or Wake-up Signal) character must be of sufficient length and be followed by a sufficient period, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

Tags: Clone Altera EPM7064BLC44-7 Programma Eeprom PLD dopo aver interrotto il bit del fusibile di protezione sul chip epm7064blc44 pld,il pacchetto di silicio di epm7064blc44 pld verrà decapsulato,Клонуйте програму Altera EPM7064BLC44-7 PLD Eeprom після обриву битового запобіжника через чіп epm7064blc44 pld,кремнієвий пакет epm7064blc44 pld буде декапсульовано,アルテラEPM7064BLC44-7PLDEepromプログラムのクローンを作成し、epm7064blc44 pldチップ上の保護ヒューズビットを切断した後、epm7064blc44pldのシリコンパッケージのカプセルを解除します。