Break NXP P89LPC921 Eeprom Heximal

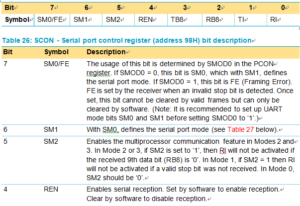

Universal Asynchronous Receiver/Transmitter can play an effective role on Break NXP P89LPC921 Eeprom Heximal. The UART operates in all standard modes. Enhancements over the standard 80C51 UART include Framing Error detection, and automatic address recognition.

MODE 0

Serial data enters and exits through RxD and TxD outputs the shift clock. Only 8 bits are transmitted or received, LSB first. The baud rate is fixed at 1¤6 of the CPU clock frequency.

UART configured to operate in this mode outputs serial clock on TxD line no matter whether it sends or receives data on RxD line.

Break NXP P89LPC921 Eeprom Heximal

MODE 1

10 bits are transmitted (through TxD) or received (through RxD): a start bit (logical 0), 8 data bits (LSB first), and a stop bit (logical 1). When data is received, the stop bit is stored in RB8 in Special Function Register SCON. The baud rate is variable and is determined by the Timer 1/2 overflow rate.

MODE 2

11 bits are transmitted (through TxD) or received (through RxD): start bit (logical 0), 8 data bits (LSB first), a programmable 9th data bit, and a stop bit (logical 1).

When data is transmitted, the 9th data bit (TB8 in SCON) can be assigned the value of 0 or (e.g. the parity bit (P, in the PSW) could be moved into TB8) from Break NXP P89LPC921 Eeprom Heximal.

When data is received, the 9th data bit goes into RB8 in Special Function Register SCON, while the stop bit is ignored. The baud rate is programmable to either 1-16 or 1-32 of the CPU clock frequency, as determined by the SMOD1 bit in PCON.

MODE 3

11 bits are transmitted (through TxD) or received (through RxD): a start bit (logical 0), 8 data bits (LSB first), a programmable 9th data bit, and a stop bit (logical 1). In fact, Mode 3 is the same as Mode 2 in all respects except baud rate. The baud rate in Mode 3 is variable and is determined by the Timer 1¤2 overflow rate.