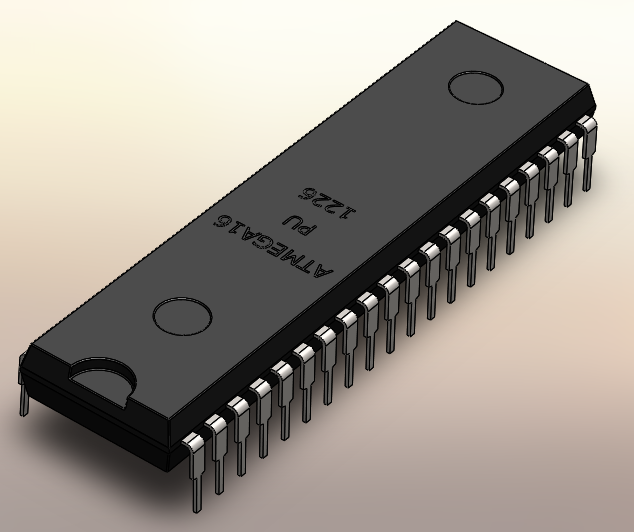

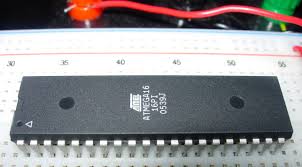

AVR Locked Microprocessor ATmega16 Flash Memory Decryption

AVR Locked Microprocessor ATmega16 Flash Memory Decryption is a process to readout embedded firmware from mcu atmega16 flash memory after cracking atmega16 secured microcontroller security fuse bit;

The memory spaces in the AVR architecture are all linear and regular memory maps. A flexible interrupt module has its control registers in the I/O space with an additional global interrupt enable bit in the Status Register. All interrupts have a separate Interrupt Vector in the Interrupt Vector table. The interrupts have priority in accordance with their Interrupt Vector posi- tion. The lower the Interrupt Vector address, the higher the priority.

The I/O memory space contains 64 addresses for CPU peripheral functions as Control Registers, SPI, and other I/O functions to attack atmega16 mcu avr flash memory. The I/O Memory can be accessed directly, or as the Data Space locations following those of the Register File, 0x20 – 0x5F.

The high-performance Atmel®AVR® ALU operates in direct connection with all the 32 general purpose working registers. Within a single clock cycle, arithmetic operations between general purpose registers or between a register and an immediate are executed by cracking atmega16 mcu flash memory. The ALU operations are divided into three main categories – arithmetic, logical, and bit-functions. Some implementa- tions of the architecture also provide a powerful multiplier supporting both signed/unsigned multiplication and fractional format. For a detailed description

Tags: атака AVR Locked Mcu ATmega16 Flash Memory,взломать AVR Locked Microprocessor Флэш-память ATmega16,разблокировать флэш-память AVR Locked Microcomputer ATmega16,сломать AVR Locked Microcontroller ATmega16 Flash Memory